Hello,

I have the following questions that I would like answered:

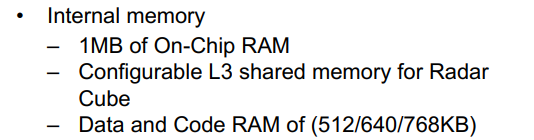

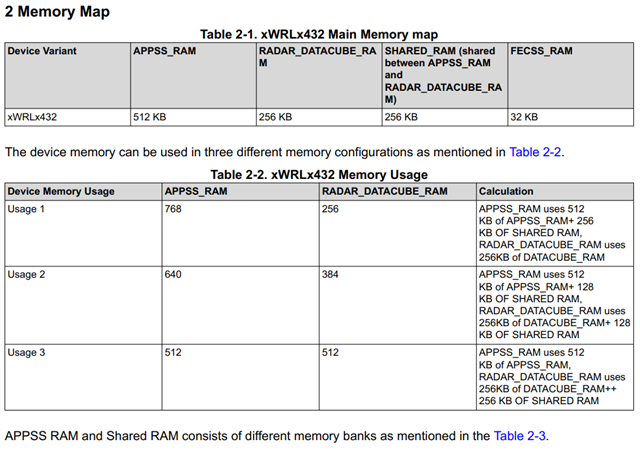

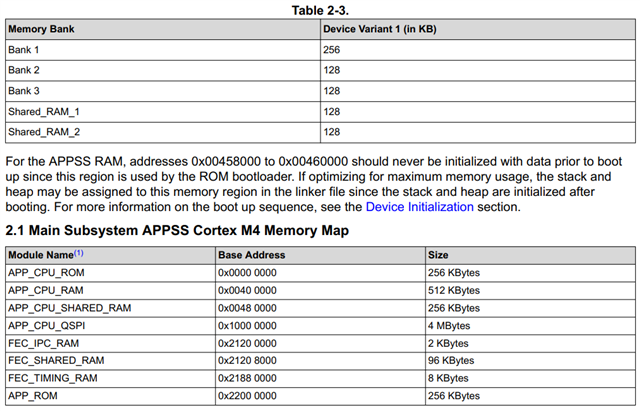

1. Generally speaking, when the chip is booted, the code and data of the external flash will be loaded into the code ram and data ram of the chip. In this chip, is there a concept of code ram and data ram? which is the corresponding memory?

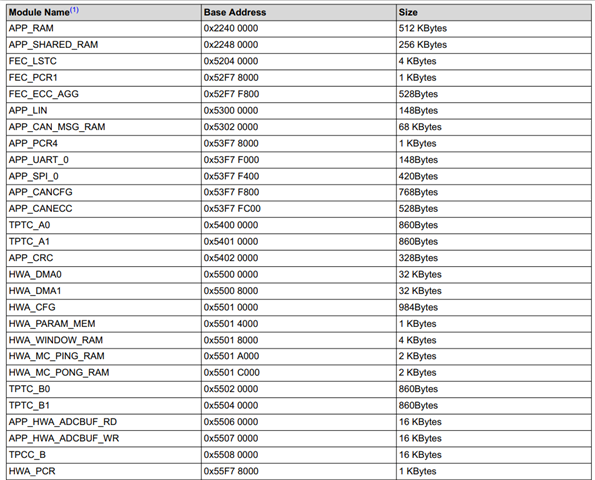

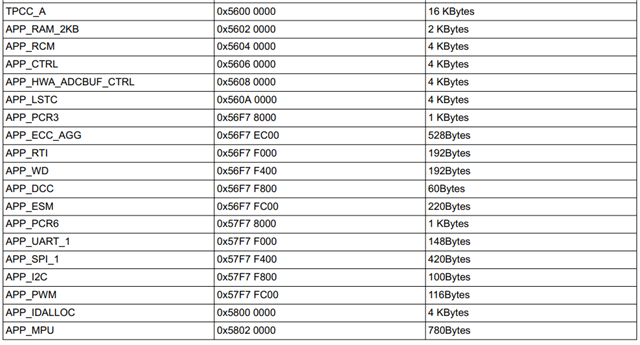

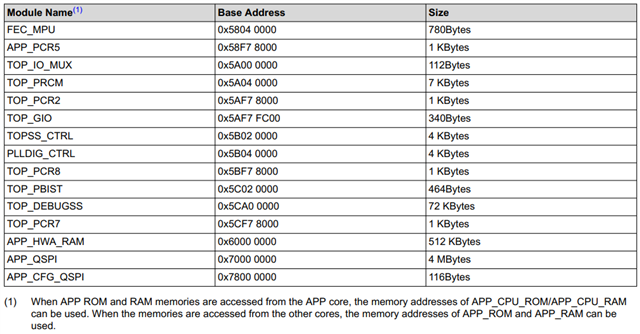

2. In the document AWRL6432 reference manual, Section 2.1,Main Subsystem APPSS Cortex M4 Memory Map, Is there any more detailed information to explain this?

3. What memory addresses can EDMA access? I tried, but the address 0x00400000 is not accessible by EDMA, but 0x22400000 is.

Looking forward to hearing from you.