作者: Amit Kumbasi

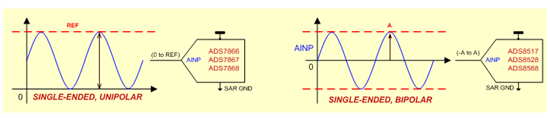

在我之前的SAR ADC输入注意事项的那一篇博文中,我介绍了针对逐次逼近寄存器 (SAR) 模数转换器 (ADC) 的不同数据类型:单端、伪差分和全差分输入。

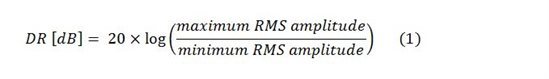

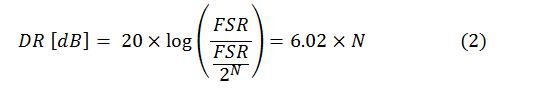

在选择一个SAR ADC时所考虑的某些关键技术规格包括分辨率、通道数量、采样率、电源范围、功耗、数字接口和时钟速度。但是诸如信噪比 (SNR) 和总谐波失真 (THD) 的噪声和AC参数是怎样的呢?这些参数会影响总体系统性能,并因此影响到SAR输入类型的选择。

噪声影响

单端输入:这些SAR只需要一条导线/电缆和一个单输入驱动器,如果有的话,连接至电源。需要注意的是,这些ADC测量相对于SAR自身接地的输入信号。虽然这是最简单的配置,信号接地和SAR接地之间的误差将影响准确度。此外,从电源和接地耦合到内部采样电容器的噪声将影响转换准确度,这是因为共模抑制 (CMRR) 很糟糕,可以忽略不计。

差分输入(伪差分和全差分):虽然这种输入需要一条额外的导线…

模拟

模拟 汽车

汽车 DLP® 技术

DLP® 技术 嵌入式处理

嵌入式处理 工业

工业 电源管理

电源管理