欢迎阅读《获得连接》系列博客!在上篇《获得连接》博客《多点应用的 LVDS》一文中,我们介绍了 TIA/EIA-899 或 MLVDS 标准以及一个典型的最终应用。本文我们将探讨串行解串器 (SerDes) 以及各种技术及其应用。

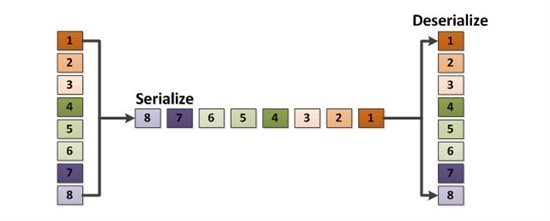

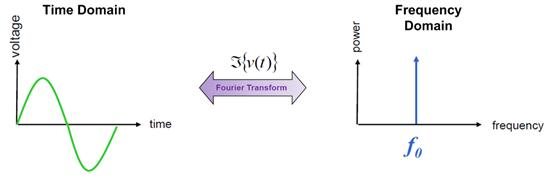

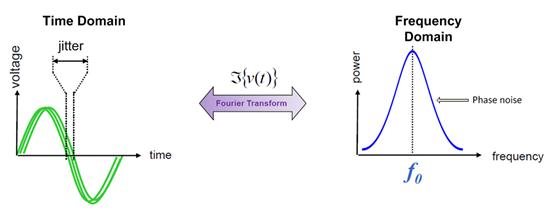

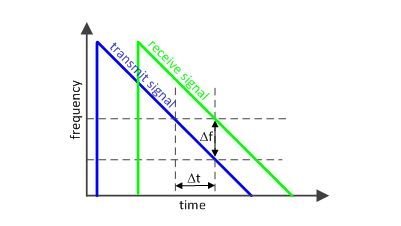

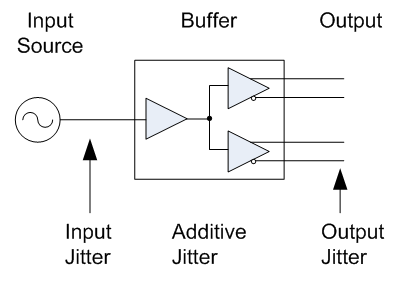

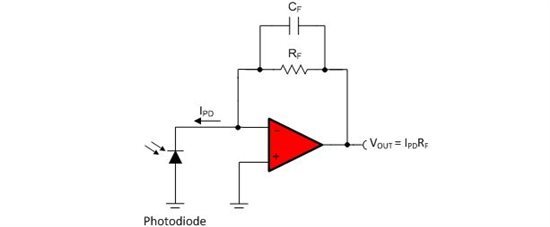

串行解串器是可将大位宽并行总线压缩成少量(通常为一条)差分串行链路的器件,该链路可在远远高于低速大位宽并行总线的速率下进行切换。串行解串器对大位宽并行总线进行了串行化,不仅可实现在系统内部、系统间或位于两个不同地点的系统间进行大量数据的点对点传输,同时还可降低功耗、板级空间和成本。下图 1 是串行解串器的基本概念。

图 1:串行∕解串

随着数据速率的增加,有关实施并行总线的问题也随之增多。较快总线比较慢总线功耗高,而且由于定时容差的降低,信道数量的增加,布局难度也越来越大。随着数据速率的增加,保持信道间的时滞也日益重要,原因是较大的时滞差异会导致系统定时问题…

模拟

模拟 汽车

汽车 DLP® 技术

DLP® 技术 嵌入式处理

嵌入式处理 工业

工业 电源管理

电源管理