TINA-TI 系列文章的本期内容主要针对第 1 部分读者所提出的需求。本文我们将了解如何生成:

- 时变(分段线性)源

- 频变源

时变源:

在实践过程中,标准波形(即方波与三角波等)可能无法满足您的仿真需求,您需要生成类似于您系统中所出现情况的真实激励波形,用以验证工作台表现或者预测构建前的性能。对于这些情况,TINA-TI 可提供能够创建瞬态或重复波形的分段线性源。

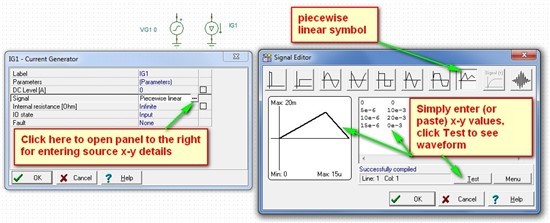

创建分段线性源的关键是,先将时间(x 轴)和电压或电流(y 轴)输入统计表格(x、y),然后将其插入 TINA-TI 源信息对话框。剩下的工作 TINA-TI 就可完成(见图 1)。

图 1:输入可定义时变波形的源(VG 或 IG)信息

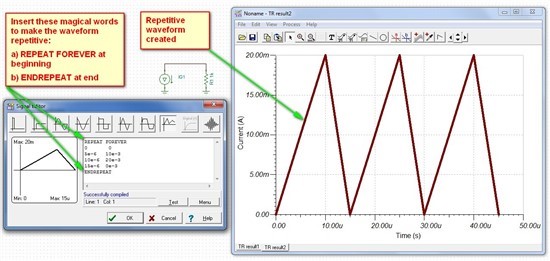

定义一个完整的 x-y 周期后,您甚至还可以让波形重复(见图 2)!

图 2:加入简单的文本命令可使波形重复

就像您看到的那样,生成单脉冲或部分波形非常容易。

…

模拟

模拟 汽车

汽车 DLP® 技术

DLP® 技术 嵌入式处理

嵌入式处理 工业

工业 电源管理

电源管理