您好,

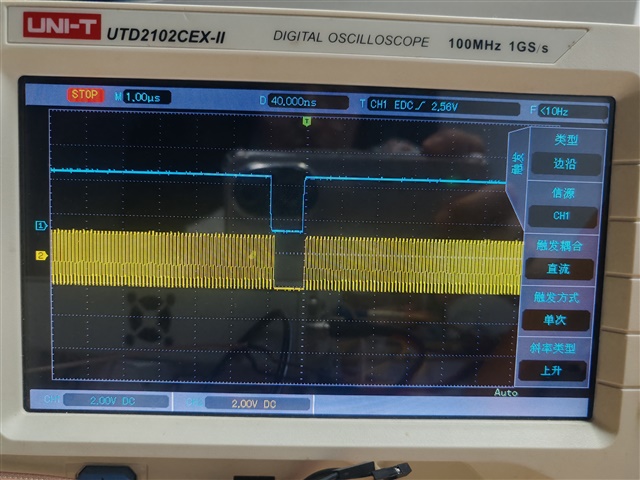

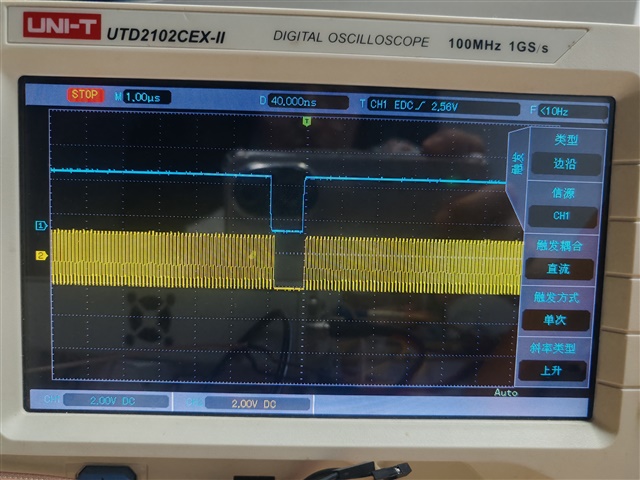

我正在验证cdce6214的时钟同步功能,当我把out1、out4的时钟勾选snyc enable,把out2、out3的时钟勾选snyc disable后,通过示波器观察out2输出的时钟信号,发现out2的时钟也受到了sync的影响,但我需要的是sync disable的信号不会受到sync信号的影响。这种现象是芯片的本来属性还是我有什么配置错误导致?

您好,

我正在验证cdce6214的时钟同步功能,当我把out1、out4的时钟勾选snyc enable,把out2、out3的时钟勾选snyc disable后,通过示波器观察out2输出的时钟信号,发现out2的时钟也受到了sync的影响,但我需要的是sync disable的信号不会受到sync信号的影响。这种现象是芯片的本来属性还是我有什么配置错误导致?

查看文档后,我对CDCE6214芯片的控制方式产生了疑惑,有以下两个问题

问题一:

芯片从R0 到 R85 共86个寄存器,每个寄存器16位,我是否可以不对EEPROM进行编程,直接写入这些寄存器完成对芯片的控制呢?

我的理解是,假如我不需要保存配置,我就不需要写入EEPROM.

问题二:

具体流程,或者配置方式是否可以简单描述一下呢?是否可以举一个实际的小例子让我明白该如何配置呢?

谢谢!

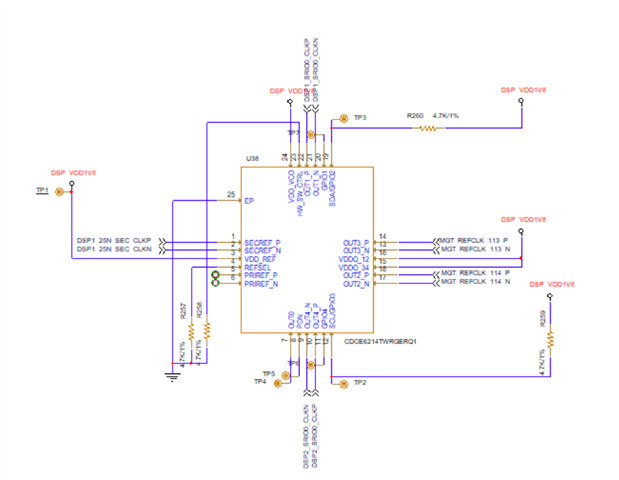

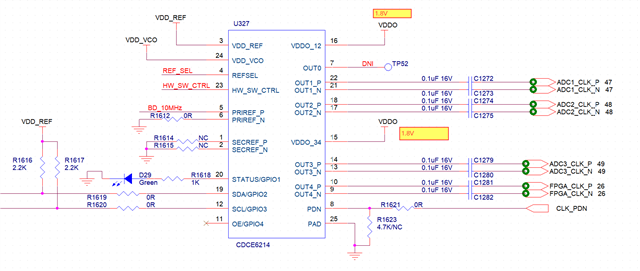

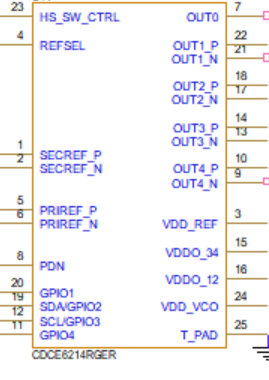

您好在使用CDCE6214时发现无法正常使用I2C总线写入cdce6214内的EEPROM,以上为我的电路连接图,请问在使用I2C写入时 是否只需要对SCL SDA进行操作,(GPIO1 GPIO4 PDN需要进行什么处理吗)。

工程师你好!

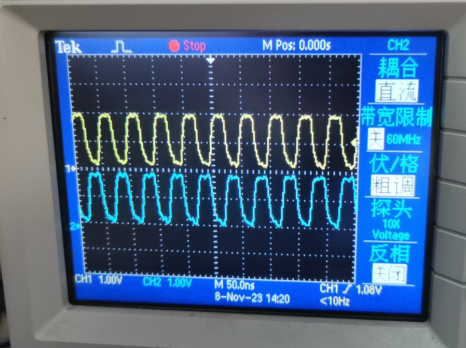

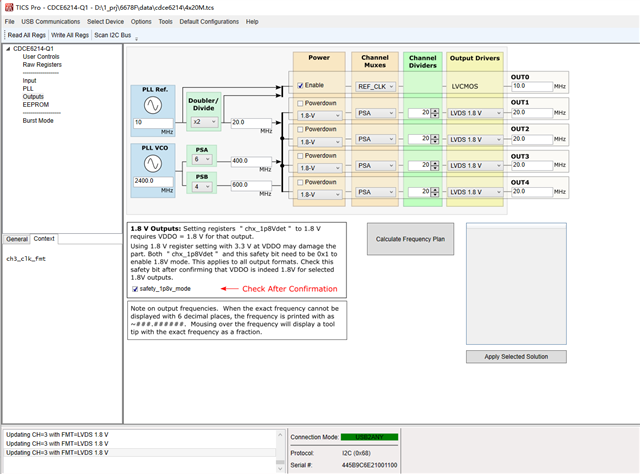

我们使用TICS Pro 配置了CDCE6214,发现LVDS 1.8V输出的摆幅有1.8V,与手册中提及的0.3V不同,请问是哪里有配置出错吗?

20MHz输出的PN差分波型:

配置:

电路:

请帮忙看下,是否有问题,感谢!

我们使用开发板,想实现输入时钟和输出时钟相位同步的功能,输入和输出时钟都是LVCMOS电平,一路输入时钟12.288M,一路输出时钟49.152M。

要求输入12.288M时钟相位变化时,输出时钟的相位也尽快调整,与输入时钟相位对齐。我们尝试了好多配置,都无法实现。除了配置wizard的内容之外,是否还需要其他配置?advance的内容如何配置…

Hi,

请问一下CDCE6214的OUT1~4支持差分时钟输出和LVCMOS时钟输出,当用作LVCMOS输出时,P/N是独立的端口。

我们场景是只需要一个LVCMOS输出,请问一下假设我们用的OUT1口输出,只开P端口和 PN都开,但只用P,从jitter等方面看有区别吗?会不会PN都开后jitter变差呢?

谢谢

你好! 这边买过CDCE6214-Q1_EVM验证完成了,但是这个demo板是通过USB烧录的,想问下工厂加工时CDCE6214-Q1如何烧录?

您好,关于CDCD6214如果我需要输出2CH LVCMOS频率,请问功耗最大是多少,在数据手持并未发现功耗的曲线

同步输出 61.44MHz和 26MHz

Hello, please take a few minutes to help me answer:

Cdce6214 uses figure 35 on Page 38 of the data manual The typical application schematic diagram of I2C interface is used for IIC communication. When the device address 0x68 is sent…