Part Number: ADC3664EVM

Other Parts Discussed in Thread: ADC3664, , ADC3664-SP

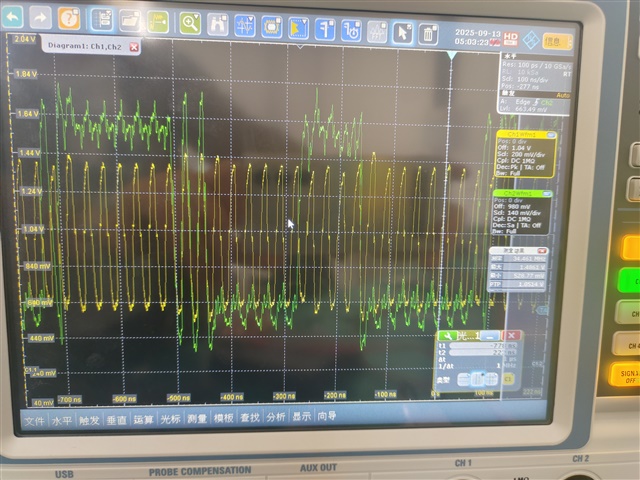

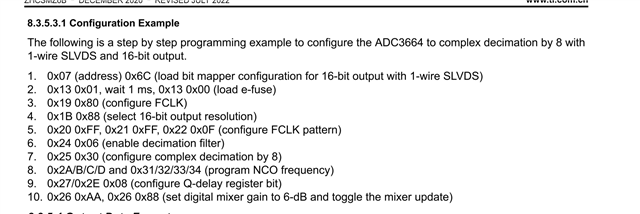

用SPI配置DDC的时候,如果不过DDC,FCLK波形正常(为占空比50%的方波);过DDC时,用示波器显示FCLK的波形占空比不规律且有些地方高电平变成低电平

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADC3664EVM

Other Parts Discussed in Thread: ADC3664, , ADC3664-SP

用SPI配置DDC的时候,如果不过DDC,FCLK波形正常(为占空比50%的方波);过DDC时,用示波器显示FCLK的波形占空比不规律且有些地方高电平变成低电平

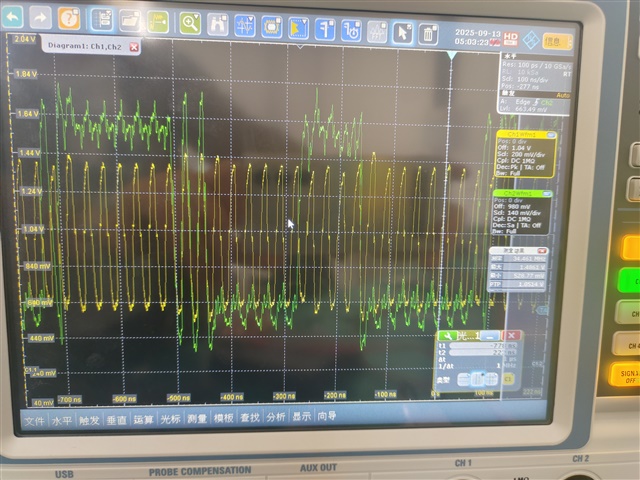

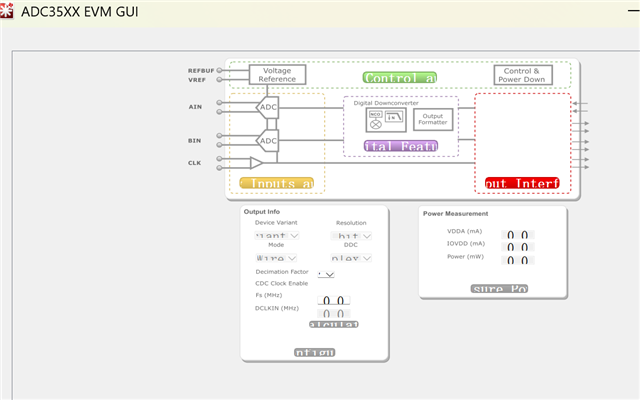

您好!我按照ADC3664EVM User's Guide “4.2.1”和“4.3.1”章节的配置示例在软件界面如图,resolution mode ddc这几项无法配置(如图1,图中这几栏为灰色,无法选择),另外我之前是用写入寄存器地址的方式配置的adc与ddc,配置的值按照adc3664的手册的样例(如图二),其中把1wire的模式改为2wire 14bit的模式,FCLK占空比配置为50%,(其他的保持和样例一致),但是出来后FCLK波形异常,我使用采样率给的10M(这是为了方便示波器观测波形,所以降低了sample clock的频率)。ad板时钟输入信号,sample clock输入为10M、DCLKIN为35M(sample clock的3.5倍)的时钟输入。

您好,

看起来您试图在Fs = 10MHz的情况下使用14位复杂八倍降采样的2线ADC。请确认这一点是否正确。

如果是的话,您的配置和DCLK是错误的。

您应该使用8.75MHz的DCLK频率。您可以使用以下公式计算您模式的正确DCLK频率:

DDC Bypass/Real Decimation:

DCLK Frequency = Sample Frequency * Resolution / Number of Wires / Decimation Factor

Complex Decimation:

DCLK Frequency = Sample Frequency * 2 * Resolution / Number of Wires / Decimation Factor

此模式的正确配置应如下所示:

0x0 0x1 // Reset

0x7 0x2b // Configure Bitmapper to 14-bit, 2 wire

0x13 0x1 // Reload efuse

0x1b 0x90 // Set output interface resolution to 14-bit

0x24 0x6 // Enable DDCs

0x25 0x30 // Configure decimation factor to 8, complex

0x27 0x10 // Set IQ Order

0x2e 0x10 // Set Q Del

0x19 0x80 // Configure FCLK settings

0x2a ???? // Set NCO A to desired freq

0x2b ???? // Set NCO A to desired freq

0x2c ???? // Set NCO B to desired freq

0x2d ???? // Set NCO B to desired freq

0x26 0x88 // NCO Reset

0x26 0xaa // NCO Reset

0x26 0x88 // NCO Reset

请忽略数据表中的配置。ADC3664数据手册存在一些已知问题,我们正在修订中。

请使用正确的DCLK频率尝试此配置,并确认FCLK是否正确。

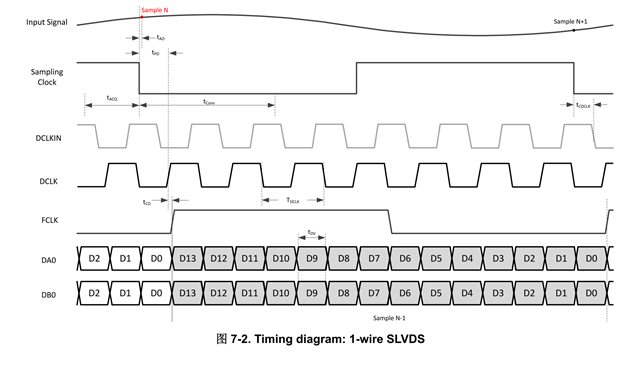

按照你给的公式,也就是所dclk受抽取率的影响,但是我想确定一下,图中为双边沿采样,也就是说,还要在公式右边整体除2。

在只过ADC的情况下:fdclk=10*14/2/1/2=35M 对应的是(依次为10M采样率, 14bit , 2wire ,bypass下为不抽取应该除1,最后的2对应的双边沿数据)

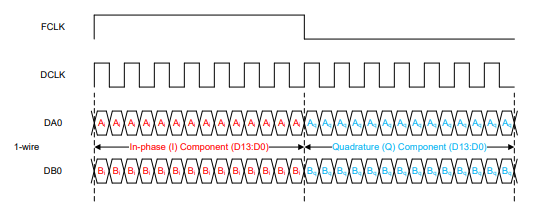

在复数模式DDC8倍抽取情况下:fdclk=10*2*14/2/8/2=8.75M 对应的是(依次为10M采样率,2复数输出, 14bit , 2wire ,ddc8倍抽取,最后的2对应的双边沿数据),你给出的频率值没错,但是是否公式需要调整,还有个问题,在复数模式下,究竟实部虚部输出的顺序是怎么样的,我知道可以通过寄存器调整,但是,在默认情况下是先实部后虚部那么和fclk有对应关系吗(例如在fclk低电平实部 高电平虚部这样的对应关系)望解答

您好,

再次建议您参考ADC3664-SP数据手册,而不是ADC3664数据手册。ADC3664-SP数据手册中的图7-32指示了I和Q数据默认如何输出。

I和Q数据的顺序可以通过寄存器配置进行交换,正如你提到的。如果你配置寄存器以交换I和Q,它们将相对于FCLK被交换,这意味着Q将会在FCLK的上升沿输出,而I将在FCLK的下降沿输出。交换I和Q不会影响FCLK,也不会改变FCLK的状态。我之前帖子中的DCLK方程是正确的。请尝试我之前帖子中的配置和DCLK,并告诉我们这是否解决了你的FCLK问题。