Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: LMK3H0102-Q1, , LMK3H0102

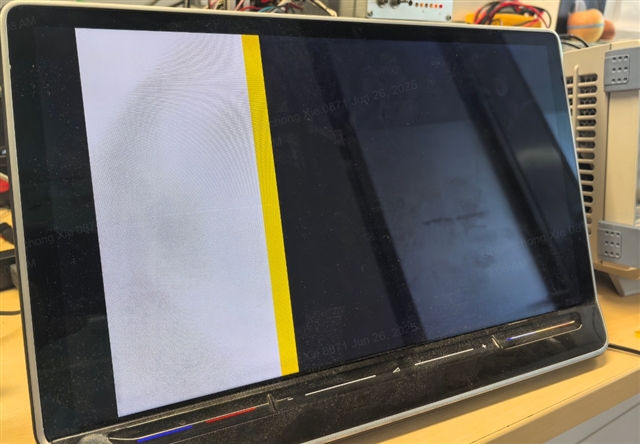

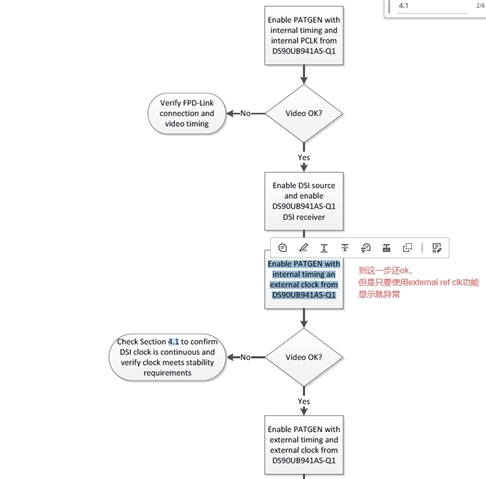

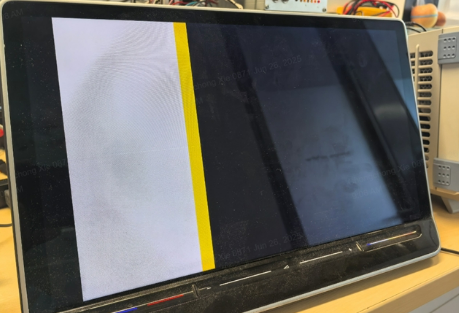

We want to try to use External Reference Clock Mode mode to light up the display on the DS90UB941 (the Ref Clk clock source comes from OUTPUT0 of the LMK3H0102-Q1 chip). What registers do we need to configure? The External DSI Clock and Ext timing we are currently using. I tried to add 0x56 to write 0x01 based on the following configuration. I don’t know if the configuration timing is incorrect, so the screen is black.

119 static struct dsi_panel_param dsi_panel_parameter[] = { 120 //15inch 121 { 122 .t_clk_post = 0x0e, 123 .t_clk_pre = 0x1e, 124 .h_active = 2240, 125 .v_active = 1260, 126 .h_front_porch = 24, 127 .h_back_porch = 40, 128 .h_sync_width = 28, 129 .v_front_porch = 6, 130 .v_back_porch = 4, 131 .v_sync_width = 2, 132 },

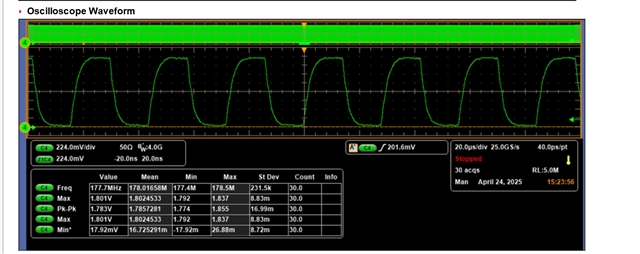

dsi clock = v total * h total * fps = (1260+6+4+2) * (2240+24+40+28) * 60 = 177,978,240 HZ

Our current DS90UB941 configuration is as follows. How to add the ref clk mode on this basis

writeLvdsRegister(0x01,0x08);

writeLvdsRegister(0x40,0x04);

writeLvdsRegister(0x41,0x05);

writeLvdsRegister(0x42,0x3C); //DPHY_SKIP_TIMING

writeLvdsRegister(0x41,0x21); //DSI_CONFIG_1

//DSI_VS_POLARITY:1->VS signal is active low;DSI_HS_POLARITY:1->HS signal is active low;DSI_NO_EOTPKT:1

writeLvdsRegister(0x42,(1<<6)|(1<<5)|(1<<0));

writeLvdsRegister(0x01,0x00);