使用两个TDP2004在一块PCB上做了TX、RX的redriver

我这边在2.7G速率自发自收测试的现象是:

当单lane时,RX侧接收TX侧发送的D10.2码型是反码,但不稳定,GT报极性错误;

当两lane时,每一个lane都应该能接收到D10.2码型,但现象是一个lane接收的D10.2码型是反码,但不稳定,GT报极性错误,另外一个lane确实乱码

原理图check之前连接技术支持邮件回复说没有问题案例编号:CS3135530

上述问题请帮忙查看

使用两个TDP2004在一块PCB上做了TX、RX的redriver

我这边在2.7G速率自发自收测试的现象是:

当单lane时,RX侧接收TX侧发送的D10.2码型是反码,但不稳定,GT报极性错误;

当两lane时,每一个lane都应该能接收到D10.2码型,但现象是一个lane接收的D10.2码型是反码,但不稳定,GT报极性错误,另外一个lane确实乱码

原理图check之前连接技术支持邮件回复说没有问题案例编号:CS3135530

上述问题请帮忙查看

您好,

在pin mode下,redriver的I2C不会响应。为了让FPGA向redriver发送I2C命令,redriver必须处于SMBus从属模式。为此,模式引脚必须通过24.9k欧姆的电阻下拉到地。

另外,您是否检查过其他速度并发现同样的问题?最后,您是否查看过布局以确认特定通道的极性没有倒置?

您好,

1.您能否给我们展示一个波形图或者分享更多细节,说明数据在某条通道上是如何出现“乱码”的?这种情况只发生在2.7G吗,还是在更高速度下也会出现?

2. I2C 应该在100到400kHz范围内工作。您使用的是7位还是8位I2C地址?数据手册中描述的是十六进制的7位I2C地址,所以如果控制器使用8位地址,则需要利用这些位来确定8位地址。例如,需要将7位地址移位,然后加1(读取)或0(写入)以从控制器执行正确的I2C操作。另外,我没有看到SDA和SCL上有上拉电阻。请检查是否在SCL和SDA上连接了上拉到VDD,否则I2C通信将无法工作。

您好,

由于 TDP2004 仅放大输入信号,我不认为这是与我们的redriver相关的问题。

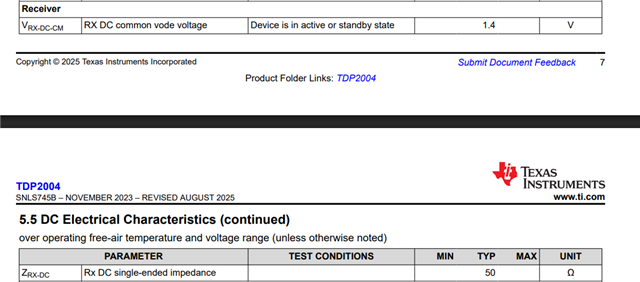

不过,建议您检查输入电压阈值是否符合数据手册要求。如果输入电压不符合要求,可能会出现这种问题,因为信号未被放大。

另外,建议您检查信号源供应商,看他们那边是否有问题。

对于 I2C,请确保检查 I2C 控制器使用的是 7 位地址还是 8 位地址。