Part Number: LSF0102

您好:

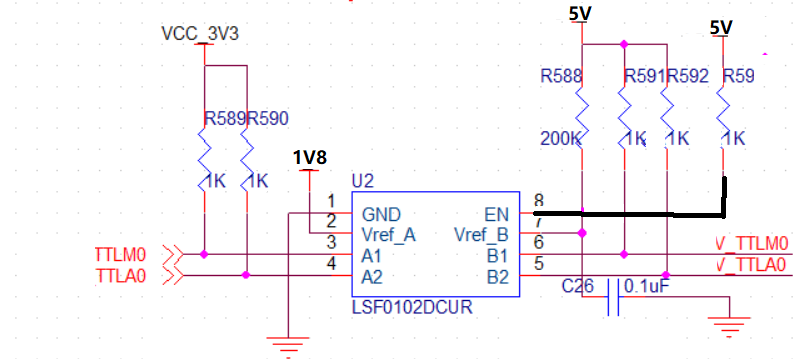

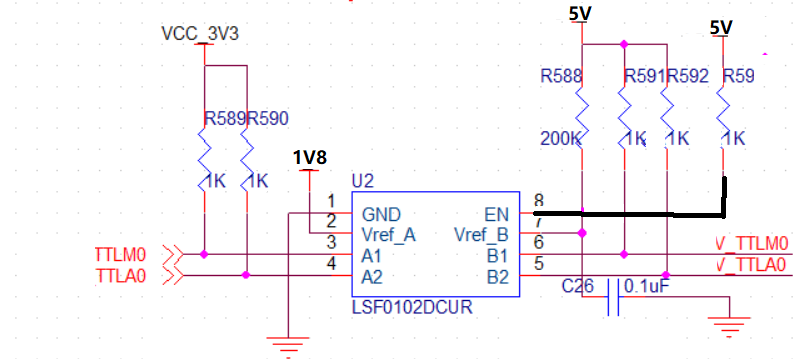

我们在使用LSF0102时,按照典型参考设计来,VREFA=2.5V、VREFB和EN连接在一起通过200K上拉到3V3,对地接0.1UF电容,然后A1/A2端信号上拉到3V3,B1/B2端信号上拉到3V3,在A侧使用FPGA的3V3bank给5M方波,在B侧测试输出波形不是正常的方波,波形在2V之后逐渐变缓慢,将电路修改成以下电路之后,电路能够正常工作,输出和输入一样,请帮忙解释第一个故障原因以及第二个电路使用的风险;

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LSF0102

您好:

我们在使用LSF0102时,按照典型参考设计来,VREFA=2.5V、VREFB和EN连接在一起通过200K上拉到3V3,对地接0.1UF电容,然后A1/A2端信号上拉到3V3,B1/B2端信号上拉到3V3,在A侧使用FPGA的3V3bank给5M方波,在B侧测试输出波形不是正常的方波,波形在2V之后逐渐变缓慢,将电路修改成以下电路之后,电路能够正常工作,输出和输入一样,请帮忙解释第一个故障原因以及第二个电路使用的风险;

感谢您对TI产品的关注。

我们正在核实您的问题,请等待我们的答复。

您好,

VREFA=2.5V、VREFB和EN连接在一起通过200K上拉到3V3,对地接0.1UF电容,然后A1/A2端信号上拉到3V3,B1/B2端信号上拉到3V3,在A侧使用FPGA的3V3bank给5M方波

请重新确认一下:VREFA为2.5V(即VCCA=2.5V),那么就应该在A侧输入2.5V的5M方波。

如果A侧是3.3V的信号,就应该VCCA=VREFA=3.3V.

同时需满足VCCA + 0.8 ≦ VCCB

EN和VREFB分开,均连接到5V或者3V3

不可以。

看您都外部加了上拉,这个信号是open-drain吗?(数据手册Figure 8-1. Typical Application Circuit for Open-Drain Translation (MDIO Shown as an Example))

您好,

VREFB和EN短接,并通过200K上拉,是为了内部调节 V_Gate,并调节从 VREFB 到 VREFA 的漏电流被调节,以确保 LSF 内部不会受到损坏。

如果您要VREFB和EN分开,那么EN脚也要使用200K上拉到相同的电源。

Top Questions About Auto Bi-Direction LSF Family Translators

您好,

LSF0102的驱动能力有限。下面帖子讨论了类似问题,请参考。

(+) LSF0102: 双向电平转换芯片实现网络MDC/MDIO电平转换,只能1对1么,是否可以实现一对多转换方式 - 逻辑论坛 - 逻辑 - E2E 设计支持