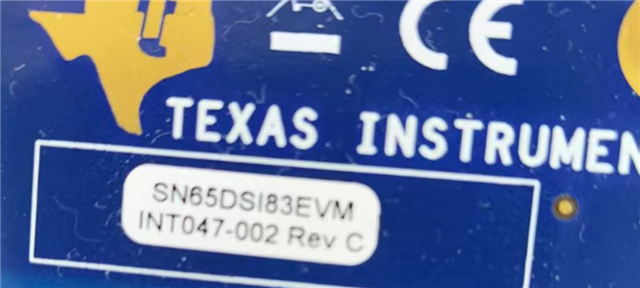

Part Number: SN65DSI83

Other Parts Discussed in Thread: SN65DSI84, SN65DSI85,

非常感谢支持,如下是问题和背景(第3点)详细描述

1、验证目标:

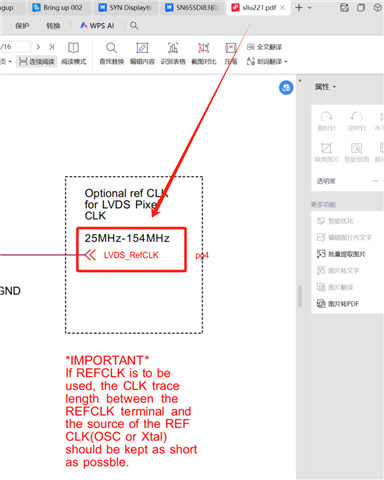

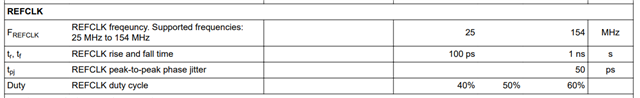

希望通过IMX8MM 初始化SN65DSI83后实现其DSI to LVDS 的功能来点亮屏幕,主要是验证转接功能,即便是屏幕不亮,如果可以验证SN65DSI83转接功能正常也可以达到验证目标。

2、问题描述

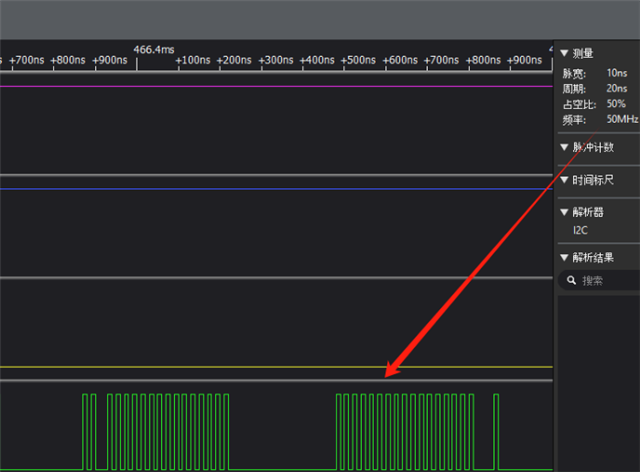

问题1: SN65DSI83 驱动报错如下log,尝试修改过lcd参数,没有任何效果,即便是屏幕不亮,有没有debug验证方法来验证 SN65DSI83转接功能是正常的?比如读写SN65DSI83哪个寄存器?或者测量哪些信号

问题2 有没有原厂屏幕的购买信息?

想要购买SN65DSI83 转接板的lcd屏幕来验证(排除lcd 屏的差异), 能否提供购买方法?

问题3 后续量产硬件连接 ,SN65DSI83 外接的不是屏幕是FPGA 的lvds 接口

SN65DSI83 现有驱动是否支持这种FPGA的连接方式?

3、如下是软硬件环境信息

3.1 硬件环境:

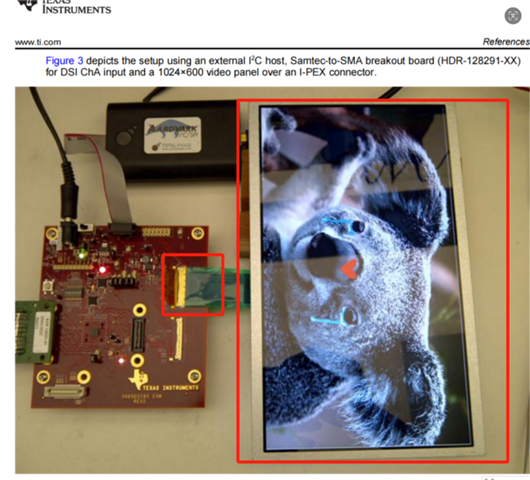

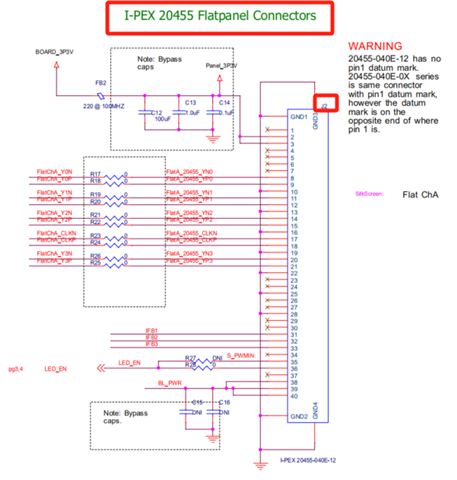

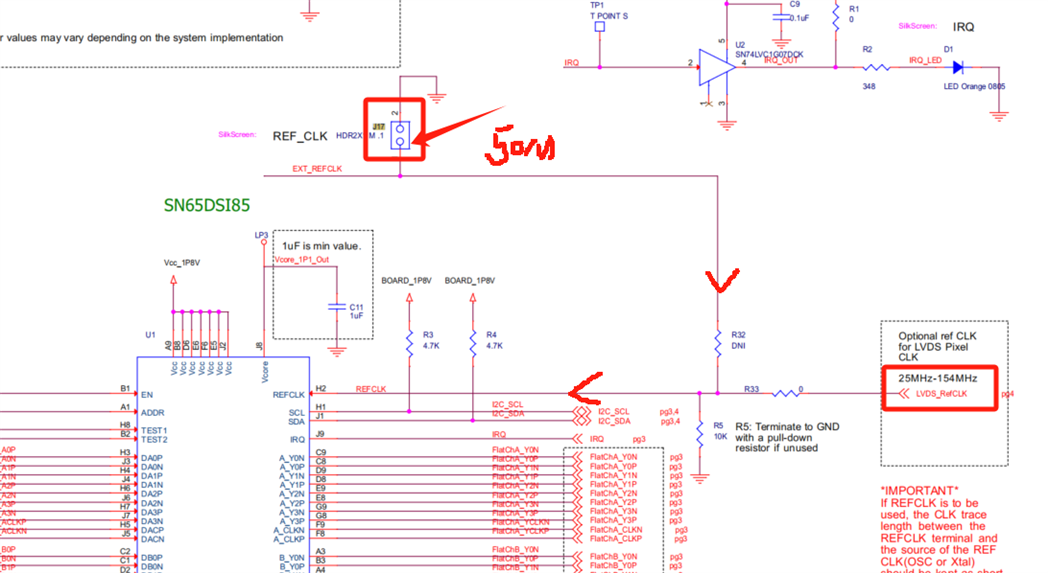

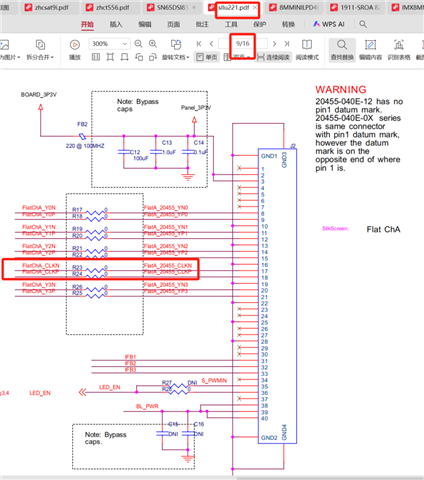

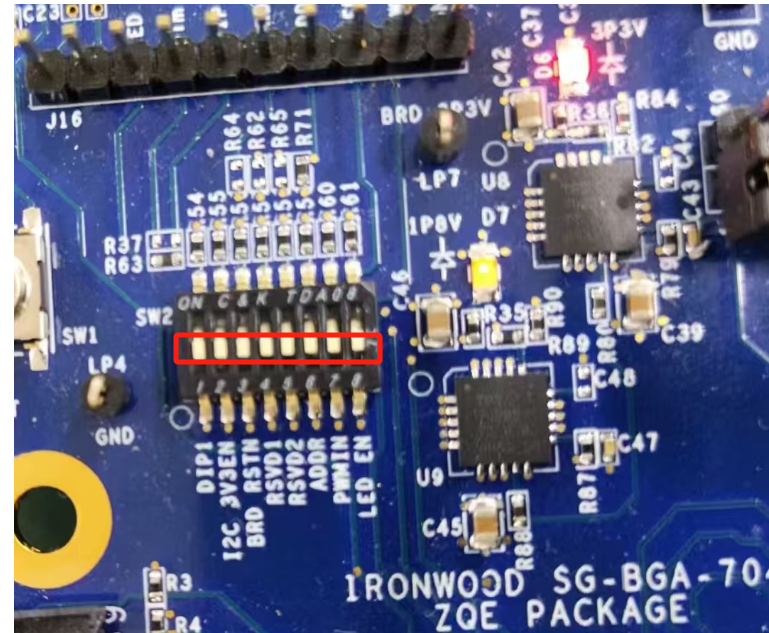

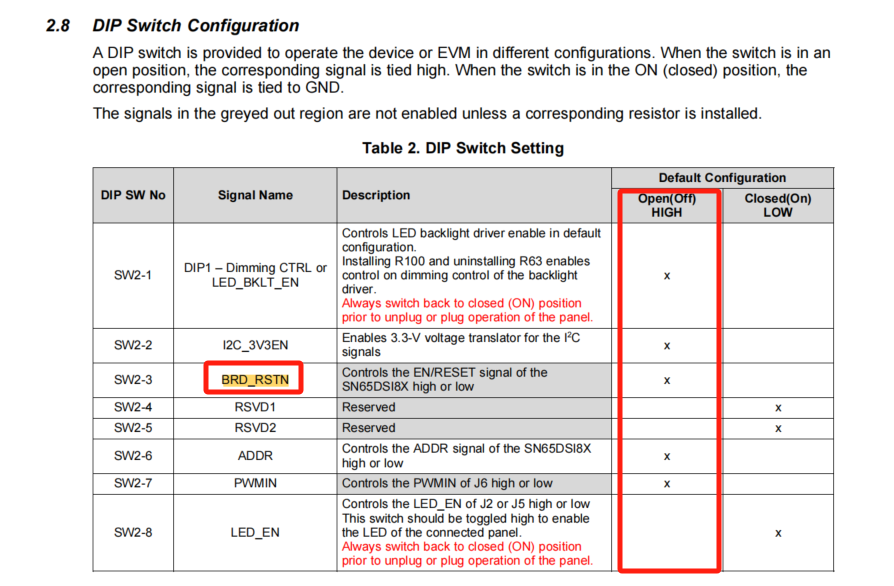

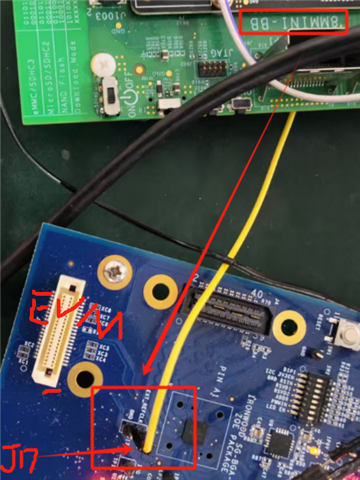

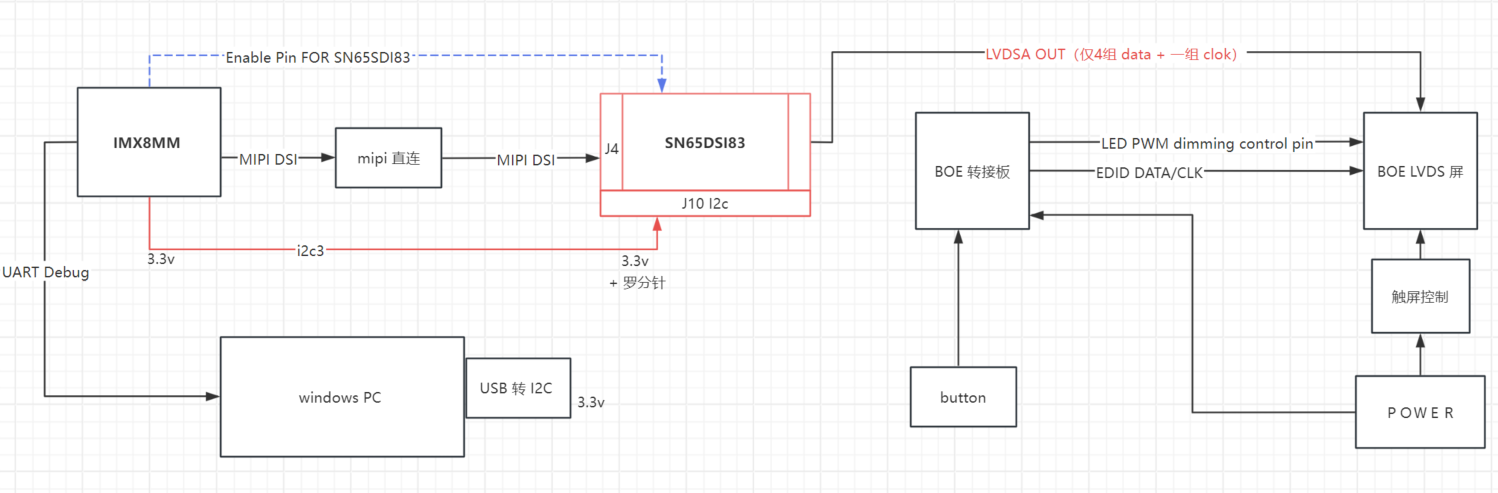

IMX8MM 开发板 MIPI DSI output 接 电平转换后再接TiSN65DSI83官方实验板再飞线接BOE 屏

Imx8侧确认硬件没有问题,换个DSI转HDMI的转接板接显示器可以出图,BOE屏单独测试可以点亮 ,如下连接设置驱动报错

环境连接拓扑如下:

没有找到和SN65DSI83 对应的原厂屏幕,所以采用的飞线的方式接BOE的屏进行测试;

3.2、软件环境:

NXP yocto 编译,LINUX 内核版本6.12

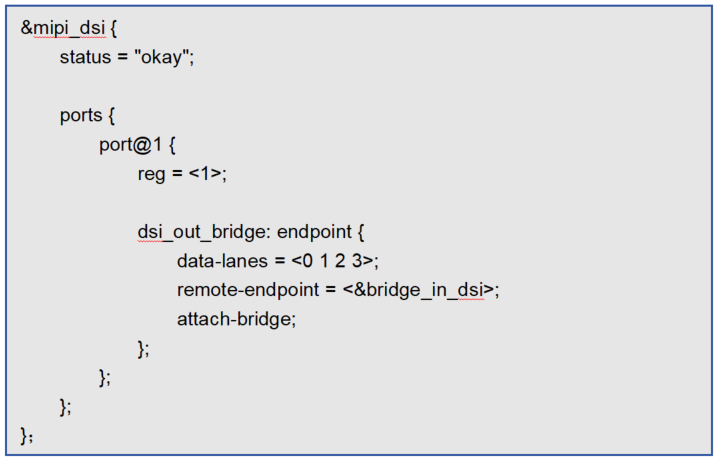

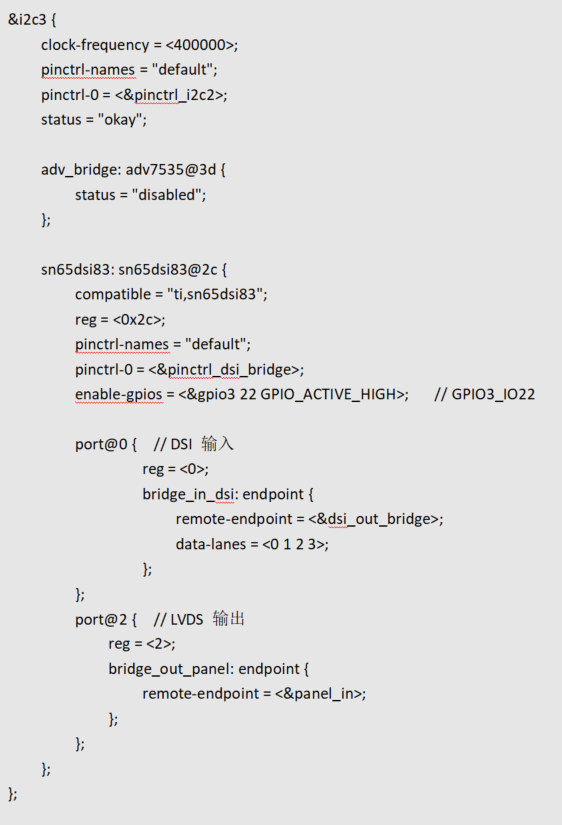

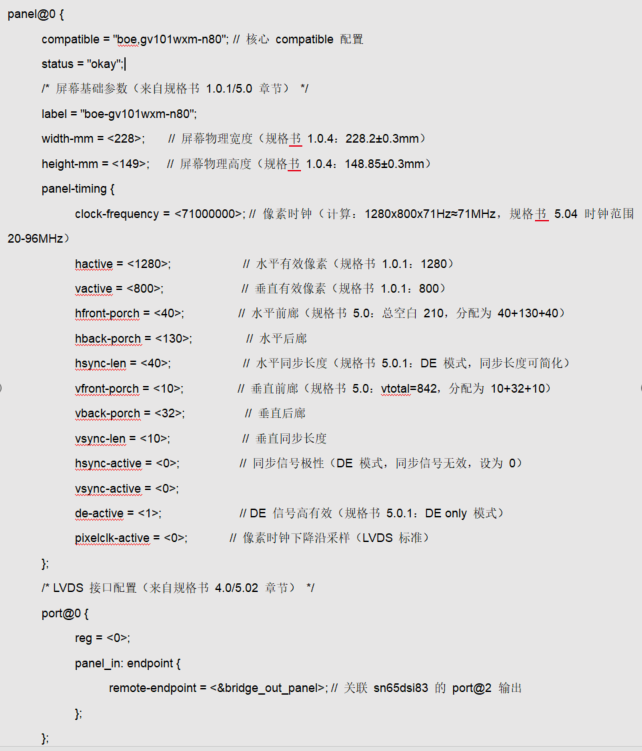

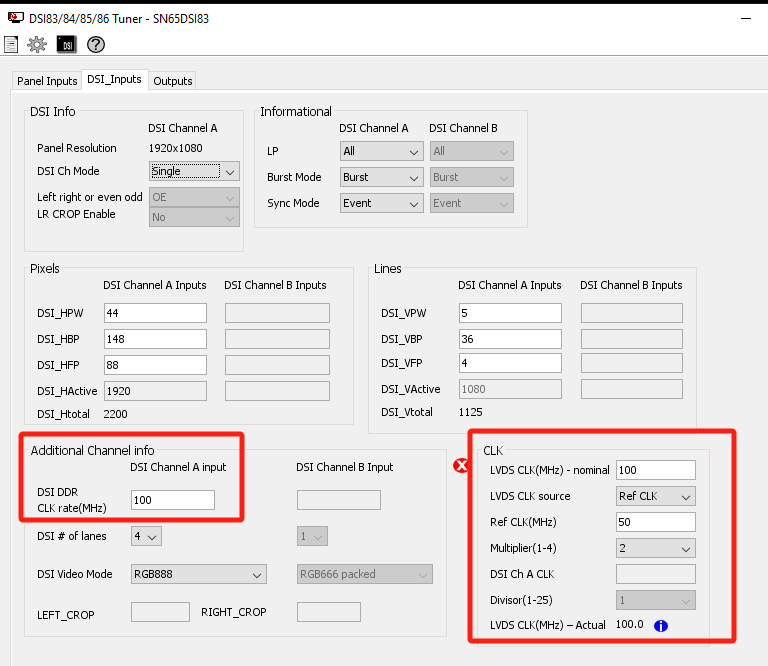

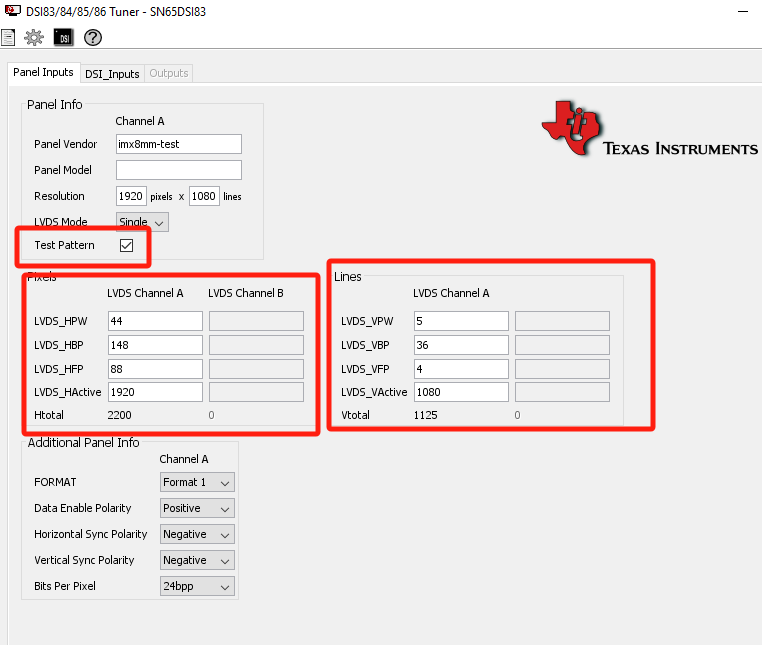

设备树配置如下