大家好~

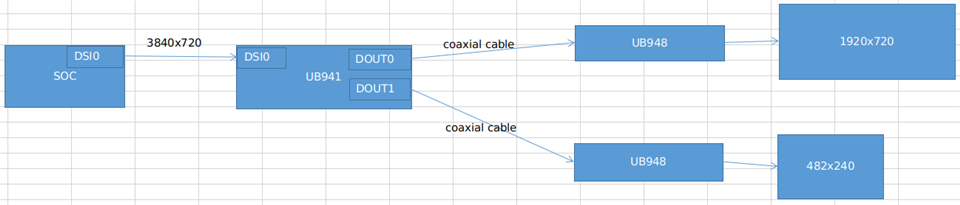

需要进行下图所示的分屏和裁剪:

Superframe(执行split之前的帧)的大小为3840x720,

使用UB941的datasheet中的“8.4.6.4.2.1 Asymmetric Splitting With Cropping”章节的方法进行分屏和对Superframe的右侧进行裁剪,

使用RevB_941AS_SuperFrame_Calc.xlsm (snlc064.zip)生成Splitting和Cropping相关的寄存器配置。

遇到的问题是1920x720的屏可以正常显示,但482x240的屏幕不能显示。

试过把Superframe的大小为3840x320并重新配置Splitting和Cropping相关的寄存器,

则482x240的屏幕显示正常,但由于高度大小1920x720的屏幕肯定就显示不正常了。

怀疑过和DOUT1输出的blanking参数有关,在Superframe配置为3840x720时做过尝试:为了使DOUT1输出的blanking能够适配482x240的屏幕,尝试修改过如下的寄存器但没有成功使482x240的屏幕显示出来(我这边对寄存器的理解也是不够,也不确定是否应该更改如下寄存器):

SPLIT_CLK_SEL, SPLIT_CLK_DIV_M, SPLIT_CLK_DIV_N

DSI_HSW_CFG_HI, DSI_HSW_CFG_LO, DSI_VSW_CFG_HI, DSI_VSW_CFG_LO

DSI_PCLK_DIV_M, DSI_PCLK_DIV_N

查看的datasheet为“DS90UB941AS-Q1 DSI to FPD-Link III Bridge Serializer datasheet (Rev. C)”。

调试时使用的Superframe的timing配置为:

uVisWidth = '3840'

uHsyncFrontPorch = '128'

uHsyncWidth = '128'

uHsyncBackPorch = '128'

uVisHeight = '720'

uVsyncFrontPorch = '3'

uVsyncWidth = '3'

uVsyncBackPorch = '3'

uPixelFreqInHz = '184757760'

bDEPolarity = '0'

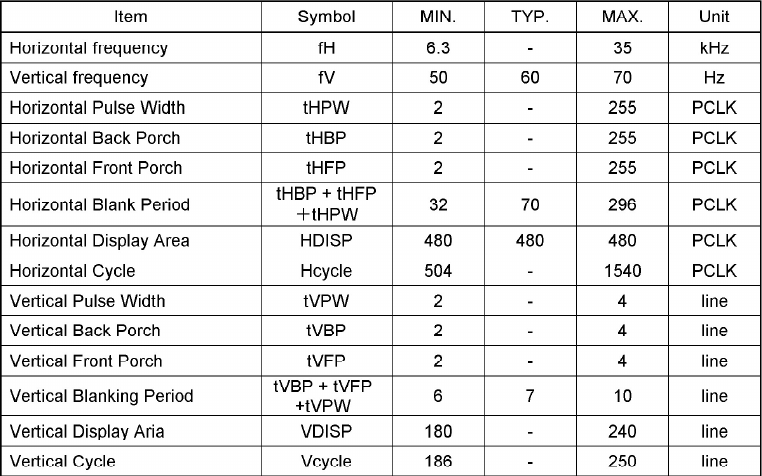

482x240的屏幕timing specification如下图:

(虽然上图中的hWidth是480,但由于bug,把hWidth设置为480会在一侧显示异常的白色竖线,所以现在设置的是482)

目前的UB941的寄存器配置如下:

| 0x01=0x08 # Disable DSI */ 0x1e=0x01 # Select FPD-Link III Port 0*/ 0x06=0x01 # Change deser i2c addr */ 0x07=0x58 0x08=0x5A 0x03=0x9a # Enable I2C_PASSTHROUGH */ 0xc6=0x21 # Step 1 of "8.3.8.1 Interrupt Pin (INTB)" from datasheet */ 0x40=0x04 # Select DSI Port 0 digital registers */ 0x41=0x21 # Select DSI_CONFIG_1 register */ 0x42=0x60 # Set DSI_VS_POLARITY=DSI_HS_POLARITY=1 */ 0x1E=0x01 # Select Port0 # set split mode, left/right 3D image, non-continuous clock mode 0x5B=0x87 # Force Splitter Mode 0x56=0x80 # Enable conversion of L/R image into alternating pixel image 0x4F=0x84 # Set 2 lane DSI 0x1E=0x02 # Select Port1 0x5B=0x87 # Force Splitter Mode 0x56=0x80 # Enable conversion of L/R image into alternating pixel image 0x4F=0x84 # Set 2 lane DSI 0x06=0x01 # Change deser i2c addr */ 0x07=0x58 0x08=0x5E 0x03=0x9a # Enable I2C_PASSTHROUGH */ 0xc6=0x21 # Step 1 of "8.3.8.1 Interrupt Pin (INTB)" from datasheet */ 0x40=0x08 # Select DSI Port 1 digital registers */ 0x41=0x21 # Select DSI_CONFIG_1 register */ 0x42=0x60 # Set DSI_VS_POLARITY=DSI_HS_POLARITY=1 */ 0x1E=0x01 # Select Port0 0x32=0x80 # Set IMG_LINE_SIZE 0x33=0x07 # Set IMG_LINE_SIZE 0x36=0x00 # Set crop start X position (LSB) 0x37=0x80 # Set crop start X position (MSB) 0x38=0x7F # Set crop stop X position (LSB) 0x39=0x07 # Set crop stop X position (MSB) 0x3A=0x00 # Set crop start Y position (LSB) 0x3B=0x00 # Set crop start Y position (MSB) 0x3C=0xCF # Set crop stop Y position (MSB) 0x3D=0x02 # Set crop start Y position (LSB) 0x1E=0x02 # Select Port1 0x36=0x00 # Set crop start X position (LSB) 0x37=0x80 # Set crop start X position (MSB) 0x38=0xE1 # Set crop stop X position (LSB) 0x39=0x01 # Set crop stop X position (MSB) 0x3A=0x00 # Set crop start Y position (LSB) 0x3B=0x00 # Set crop start Y position (MSB) 0x3C=0xEF # Set crop stop Y position (MSB) 0x3D=0x00 # Set crop start Y position (LSB) 0x1E=0x01 # Select Port0 0x40=0x04 # Select DSI digital page 0x41=0x05 # To reg 0x05 (TSKIP CNT) 0x42=0x36 # Set value for DSI+CLK 0x40=0x08 # Select DSI digital page 0x41=0x05 # To reg 0x05 (TSKIP CNT) 0x42=0x36 # Set value for DSI+CLK 0x01=0x00 # Enable DSI */ |

现有如下问题:

1. 按第1个图那样进行分屏和裁剪后,UB941的datasheet中说的意思我理解是vertical blanking会变的很大,但具体变为什么样子我不太清楚,所以请问DOUT1输出的display timing / blanking的值是怎样的?

2. UB941支持对DOUT1输出的display timing / blanking进行修改吗?支持的话如何配置?

3. 还需要做什么才能使两个屏幕都能正常显示?