Other Parts Discussed in Thread: TSB82AA2B, XIO2001

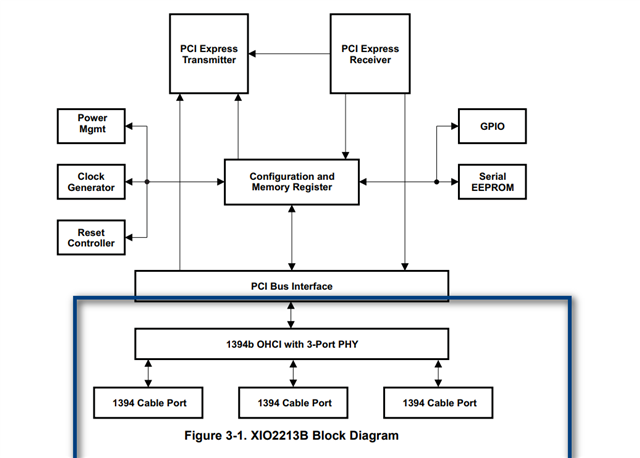

你好,我想用XIO2213B实现PCIE到1394b的转换,在官网上找到了XIO2213的评估板,关于评估板有几个疑问:

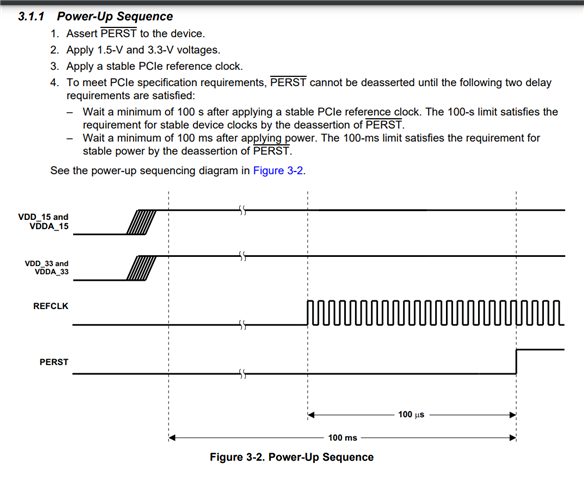

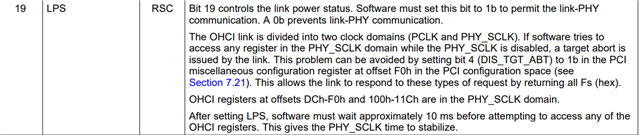

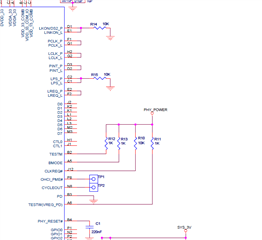

1.关于上电顺序:我看到XIO2213数据手册中建议PERST先置低,在给芯片供电;但是评估板中的供电芯片使能引脚是直接写死的,评估板没有按照芯片数据手册中的上电顺序执行?不影响芯片正常使用吗?

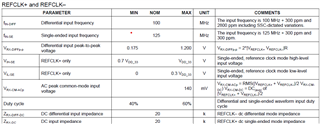

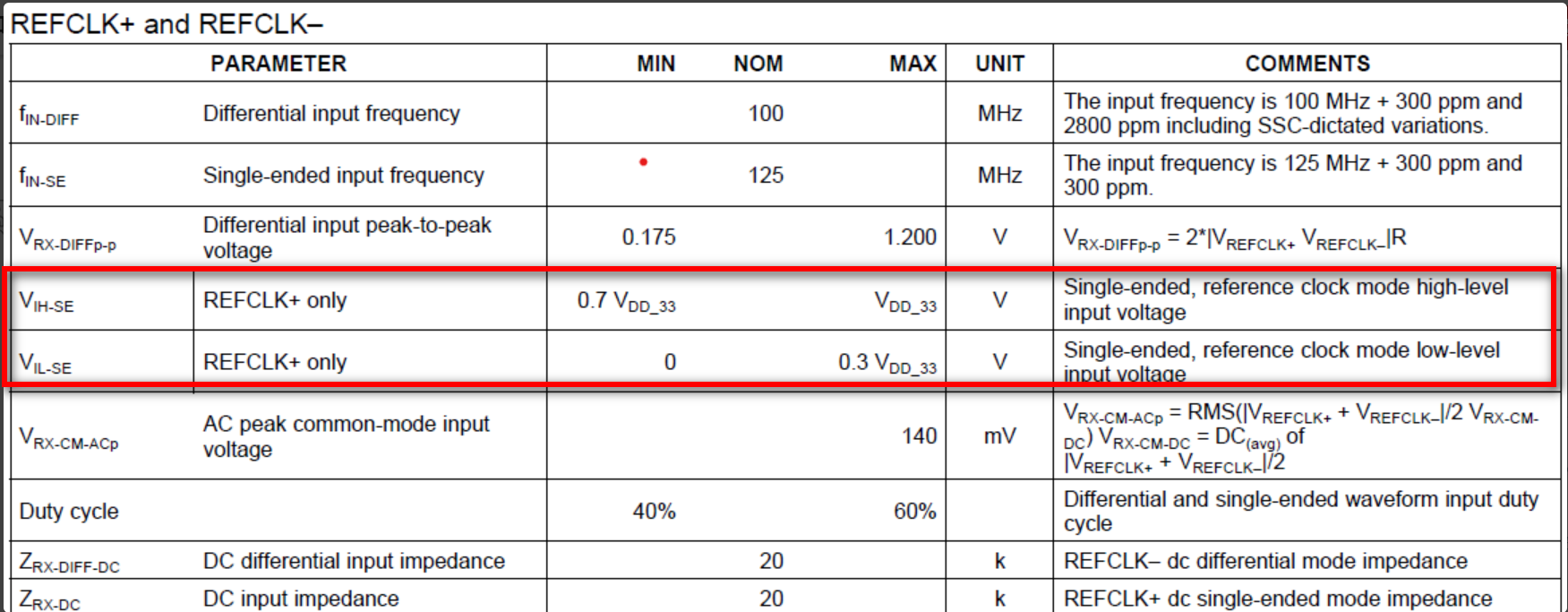

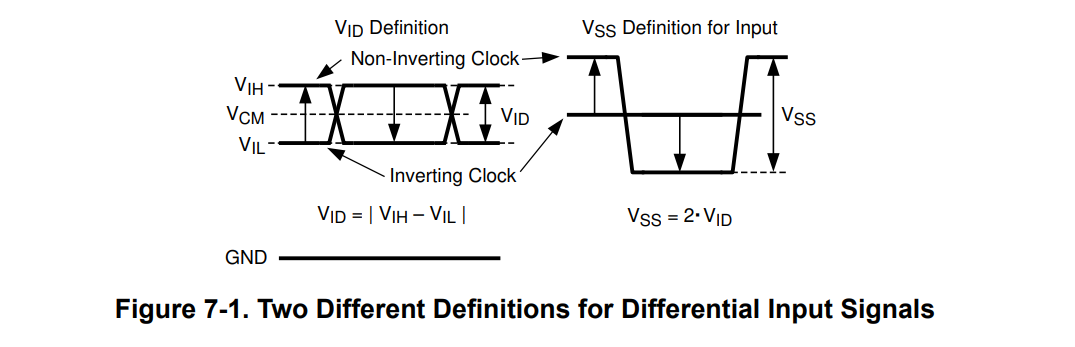

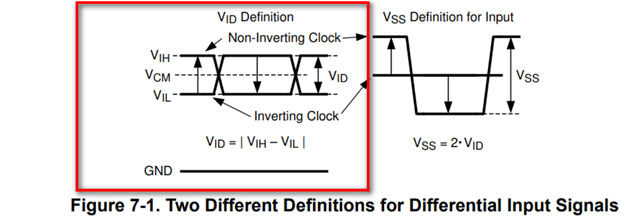

2.PCIE接口RXP/RXN引脚应用手册中建议采用交流耦合,请问是芯片引脚内部有直流偏置吗?如果我使用直流耦合,可接受的直流偏置电压范围是多少呢?数据手册中只有差模输入范围,未给处直流偏置电压范围。

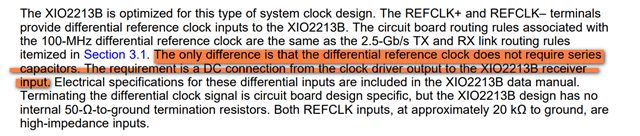

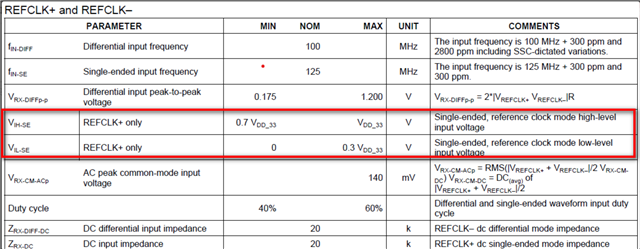

3.REFCLK+/REFCLK-这两个引脚在应用手册中推荐使用直流耦合,请问可接受的直流偏置电压范围是多少呢?数据手册中也是只有差模输入范围,未给处直流偏置电压范围。

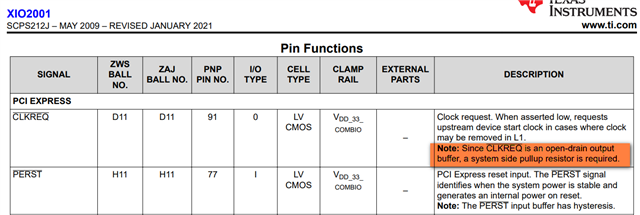

4.CLKREQ在数据手册中被定义为输出,但是评估板中对它进行了外部上拉,芯片内部是类似于OC?没在数据手册中找到引脚输出示意图和相关介绍。

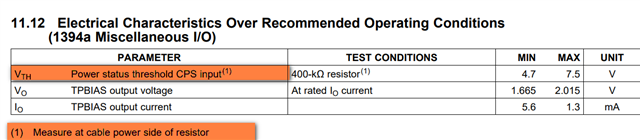

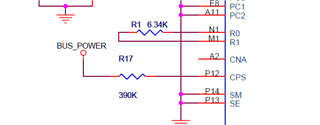

5.CPS引脚:数据手册中推荐使用一个400k的电阻接到该引脚和cable power两端,但是在数据手册的第11.12章给定的推荐Vth电压为4.7~7.5V,请问这个电压范围是对cable power的约束吗?如果是,我看到评估板中的cable power是12V;如果不是,这个Vth的具体含义是什么?另外,cable power大于多少时,会损坏芯片?

6.LPS_L和LPS_P在外部短接后,为什么要在加入一个下拉电阻?没有在数据手册和使用手册中找到相关描述。

7.CTL0/CTL1/D[7:0]为什么在评估板上被悬空了?我在tsb81ba3和tsb82aa2b的数据手册中找到了这些引脚是1394LLC和PHY的控制总线和数据总线,如果我使用tsb81ba3和tsb82aa2b进行设计,这两个芯片的这些引脚必须互连用于数据传输。那为什么在XIO2213中会被悬空,他们在芯片内部已经把LLC和PHY互连了吗?

以上就是我关于XIO2213评估板的一些疑问,问题有点多,麻烦了~