Part Number: DS90UB941AS-Q1

链路: soc - 943+948 - dp

问题:偶现闪屏,且闪屏时会出现界面偏移

详细描述:所用timing自刷图是OK的,然后用此timing写入发现偶现闪屏,其中pclk经计算正常

想要get间接寄存器的值 但是获取的一值是0,应该是我方式不对

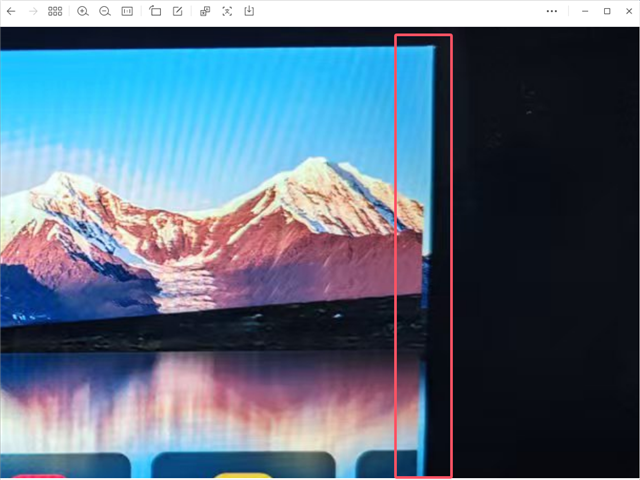

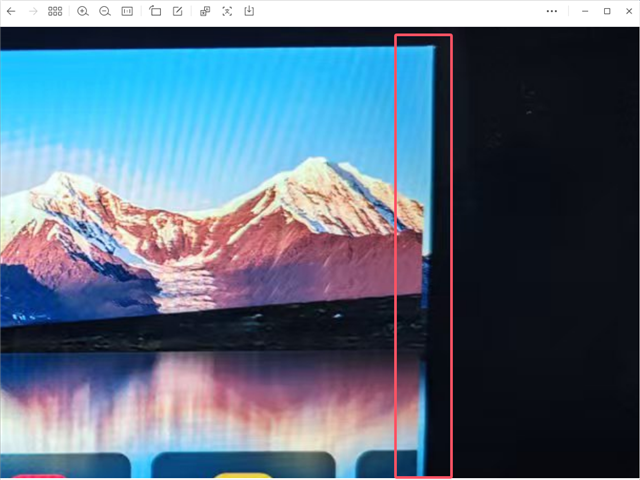

其中界面偏移的图片如下:

在不闪屏时 无偏移

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB941AS-Q1

链路: soc - 943+948 - dp

问题:偶现闪屏,且闪屏时会出现界面偏移

详细描述:所用timing自刷图是OK的,然后用此timing写入发现偶现闪屏,其中pclk经计算正常

想要get间接寄存器的值 但是获取的一值是0,应该是我方式不对

其中界面偏移的图片如下:

在不闪屏时 无偏移

您好!

谁是客户 Tier1/EOM

这是哪个项目?

有多少系统出现了此问题?

故障率是多少?

这是上电问题还是运行时问题(一段时间后发生?)

您当前正在使用哪个脚本生成版本?

您在使用哪种 SoC?

请发送 SERDES 初始化代码以供审核。

您好,

我这边是移远 +t1四维+主机厂大通 共同咨询此问题

这个是大通的项目

目前有多个车机系统出现这个问题,非一个

上电时就开始发生闪屏

当前使用版本未知,但我直接提供了pll的设置

使用的是6125芯片

SERDES 初始化代码如下:

////////////////////////////////////////////////////////////////////////////.ds90ub943_apb_config

REG_VALUE3(serAddr,0x01,0x40);

REG_VALUE3(serAddr,0x48,0x1); //Enable APB Interface

REG_VALUE3(serAddr,0x49,0x0); //Force HPD low to configure 983 DP settings

REG_VALUE3(serAddr,0x4a,0x0);

REG_VALUE3(serAddr,0x4b,0x0);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

REG_VALUE3(serAddr,0x49,0x74); //Set max advertised link rate = 2.7Gbps

REG_VALUE3(serAddr,0x4a,0x0);

REG_VALUE3(serAddr,0x4b,link_rate);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

REG_VALUE3(serAddr,0x49,0x70); //Set max advertised lane count = 2

REG_VALUE3(serAddr,0x4a,0x0);

REG_VALUE3(serAddr,0x4b,link_lanes);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

REG_VALUE3(serAddr,0x49,0x14); //Request min VOD swing of 0x02

REG_VALUE3(serAddr,0x4a,0x2);

REG_VALUE3(serAddr,0x4b,0x2);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

REG_VALUE3(serAddr,0x49,0x18); //Set SST/MST mode and DP/eDP Mode

REG_VALUE3(serAddr,0x4a,0x0);

REG_VALUE3(serAddr,0x4b,0x14);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

REG_VALUE3(serAddr,0x49,0x0); //Force HPD high to trigger link training

REG_VALUE3(serAddr,0x4a,0x0);

REG_VALUE3(serAddr,0x4b,0x1);

REG_VALUE3(serAddr,0x4c,0x0);

REG_VALUE3(serAddr,0x4d,0x0);

REG_VALUE3(serAddr,0x4e,0x0);

//////////////////////////////////////////////////////////////////////////.ds90ub943_set_port_config

REG_VALUE3(serAddr,0x07,0x89); // Set FPD III Mode

REG_VALUE3(serAddr,0x05,0x80); // Set FPD III Mode

REG_VALUE3(serAddr,0x59,0x3);

////////////////////////////////////////////////////////////////////////.ds90ub943_set_pll_config

den=16776936

num=6617569

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x05),

REG_VALUE3(serAddr, 0x42, 0x74), //#write to register 0x05

REG_VALUE3(serAddr, 0x42, 0x00), //#write to register 0x06

//#Denominator set to 16776990

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x18),

REG_VALUE3(serAddr, 0x42, (den>>0)&0xff), //#write to register 0x18

REG_VALUE3(serAddr, 0x42, (den>>8)&0xff), //#write to register 0x19

REG_VALUE3(serAddr, 0x42, (den>>16)&0xff), //#write to register 0x1a

//#Numerator set to 1180603

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x1e),

REG_VALUE3(serAddr, 0x42, (num>>0)&0xff), //#write to register 0x1e

REG_VALUE3(serAddr, 0x42, (num>>8)&0xff), //#write to register 0x1f

REG_VALUE3(serAddr, 0x42, (num>>16)&0xff), //#write to register 0x20

//#Post-divider set to 8 and auto VCO selection enabled

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x13),

REG_VALUE3(serAddr, 0x42, 0xf0), //#write to register 0x13 default auto

//#SSCG disabled

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x17),

REG_VALUE3(serAddr, 0x42, 0x00), //#write to register 0x17

//#SSCG spread type set to center-spread (required when SSCG is disabled),

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x14),

REG_VALUE3(serAddr, 0x42, 0x80), //#write to register 0x14

//#PLL order set to fractional

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x04),

REG_VALUE3(serAddr, 0x42, 0x09), //#write to register 0x04

//#Programs FPD-Link PLL for 98x device to 1.567 Gbps (PCLK is 44.770 MHz),

//#PLL script revision: 0

//#Configuring PLL1 (Port 1),

//#uses fixed I2C address

//#N-divider set to 116

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x45),

REG_VALUE3(serAddr, 0x42, 0x74), //#write to register 0x45

REG_VALUE3(serAddr, 0x42, 0x00), //#write to register 0x46

//#Denominator set to 16776990

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x58),

REG_VALUE3(serAddr, 0x42, (den>>0)&0xff), //#write to register 0x18

REG_VALUE3(serAddr, 0x42, (den>>8)&0xff), //#write to register 0x19

REG_VALUE3(serAddr, 0x42, (den>>16)&0xff), //#write to register 0x1a

//#Numerator set to 1180603

REG_VALUE3(serAddr, 0x40, 0x0a),

REG_VALUE3(serAddr,0x41, 0x5e),

REG_VALUE3(serAddr, 0x42, (num>>0)&0xff), //#write to register 0x1e

REG_VALUE3(serAddr, 0x42, (num>>8)&0xff), //#write to register 0x1f

REG_VALUE3(serAddr, 0x42, (num>>16)&0xff), //#write to register 0x20

//#Post-divider set to 8 and auto VCO selection enabled

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x53),

REG_VALUE3(serAddr, 0x42, 0xf0), //#write to register 0x53

//#SSCG disabled

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x57),

REG_VALUE3(serAddr, 0x42, 0x00), //#write to register 0x57

//#SSCG spread type set to center-spread (required when SSCG is disabled),

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x54),

REG_VALUE3(serAddr, 0x42, 0x80), //#write to register 0x54

//#PLL order set to fractional

REG_VALUE3(serAddr, 0x40, 0x08),

REG_VALUE3(serAddr,0x41, 0x44),

REG_VALUE3(serAddr, 0x42, 0x09), //#write to register 0x44

REG_VALUE3(serAddr,0x1,0x30); //PLL Reset

MSLEEP(10);

REG_VALUE3(serAddr,0x40,0x4); //Set FPD Page to configure BC Settings for Port 0 and Port 1

REG_VALUE3(serAddr,0x41,0x6);

REG_VALUE3(serAddr,0x42,0xff);

REG_VALUE3(serAddr,0x41,0xd);

REG_VALUE3(serAddr,0x42,0x70);

REG_VALUE3(serAddr,0x41,0xe);

REG_VALUE3(serAddr,0x42,0x70);

REG_VALUE3(serAddr,0x41,0x26);

REG_VALUE3(serAddr,0x42,0xff);

REG_VALUE3(serAddr,0x41,0x2d);

REG_VALUE3(serAddr,0x42,0x70);

REG_VALUE3(serAddr,0x41,0x2e);

REG_VALUE3(serAddr,0x42,0x70);

REG_VALUE3(serAddr,0x1,0x30); //Reset PLLs

////////////////////////////////////////////////////////////////////ds90ub943_set_vp_timing

REG_VALUE3(serAddr,0x40,0x32);

REG_VALUE3(serAddr,0x41,0x1);

REG_VALUE3(serAddr,0x42,0x20); //Set VP_SRC_SELECT to Stream 0 for SST Mode

REG_VALUE3(serAddr,0x41,0x2);

REG_VALUE3(serAddr,0x42,0x80); //VID H Active

REG_VALUE3(serAddr,0x42,0x7); //VID H Active

REG_VALUE3(serAddr,0x41,0x10);

REG_VALUE3(serAddr,0x42,0x80); //Horizontal Active

REG_VALUE3(serAddr,0x42,0x7); //Horizontal Active

REG_VALUE3(serAddr,0x42,0x30); //Horizontal Back Porch

REG_VALUE3(serAddr,0x42,0x0); //Horizontal Back Porch

REG_VALUE3(serAddr,0x42,0x28); //Horizontal Sync

REG_VALUE3(serAddr,0x42,0x0); //Horizontal Sync

REG_VALUE3(serAddr,0x42,0x8); //Horizontal Total

REG_VALUE3(serAddr,0x42,0x8); //Horizontal Total

REG_VALUE3(serAddr,0x42,0xd0); //Vertical Active

REG_VALUE3(serAddr,0x42,0x2); //Vertical Active

REG_VALUE3(serAddr,0x42,0x2); //Vertical Back Porch

REG_VALUE3(serAddr,0x42,0x0); //Vertical Back Porch

REG_VALUE3(serAddr,0x42,0x2); //Vertical Sync

REG_VALUE3(serAddr,0x42,0x0); //Vertical Sync

REG_VALUE3(serAddr,0x42,0x4); //Vertical Front Porch

REG_VALUE3(serAddr,0x42,0x0); //Vertical Front Porch

REG_VALUE3(serAddr,0x41,0x27);

REG_VALUE3(serAddr,0x42,0x06); //HSYNC Polarity = -, VSYNC Polarity = -

///////////////////////////////////////////////////////////////////////ds90ub943_enable_vp

REG_VALUE3(serAddr,0x43,0x0); //Set number of VPs used = 1

REG_VALUE3(serAddr,0x44,0x1); //Enable video processors

////////////////////////////////////////////////////////////////////////////ds90ub943_set_stream

REG_VALUE3(serAddr,0x2d,0x1); //Select FPD TX Port 0

REG_VALUE3(serAddr,0x57,0x0); //Set FPD TX Port 0 Stream Source = VP0

REG_VALUE3(serAddr,0x2d,0x12); //Select FPD TX Port 1

REG_VALUE3(serAddr,0x57,0x0); //Set FPD TX Port 1 Stream Source = VP0

REG_VALUE3(serAddr,0x5b,0x2b); //Enable FPD III FIFO

REG_VALUE3(serAddr,0x2,0xf0); //CRC Error Reset

REG_VALUE3(serAddr,0x2,0xd1); //CRC Error Reset Clear

REG_VALUE3(serAddr,0x2d,0x1);

您好!

您能否提供此处使用的视频时序?

THW[0] = ?

TVW[0] = ?

AHW[0] = ?

AVW[0] = ?

HBP[0] = ?

VBP[0] = ?

HSW[0] = ?

VSW[0] = ?

HFP[0] = ?

VFP[0] = ?

HSP[0] = ?

VSP[0] = ?

PCLK[0] =?

Bits_per_pixel[0] = ?

这是单路还是双路 FPD 模式? 这里的 FPD 比率是多少?

您是否尝试过运行 SERDES Patgen? 相同的问题是出现在 SER 和 DES PATGEN 中还是仅出现在 SoC 视频中?

您发现此问题的频率如何? 总是、有时、很少?