Part Number: SN74HCS08

Hi,

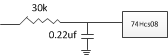

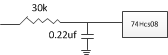

We use 74hcs serie chips to solve the slow rise/fall time issue, because RC(R:30K C:0.22uf) is designed as the input of 74hcs08 to have a certain delay time.

We belive that the solw rise time is suitable for hcs chips as the datesheet described:

However, the slow rise/fall siganl may failue to triggle the 74hcs08.

What is the problem of this design?

Thanks very much!