主题中讨论的其他器件: THS3215、 THS3217、 OPA838

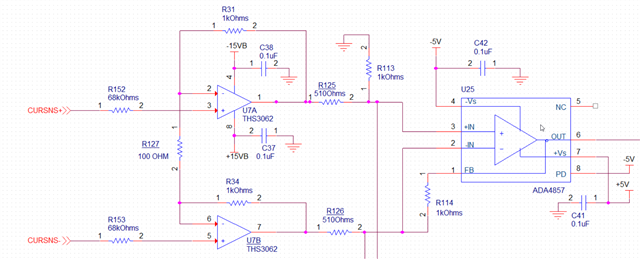

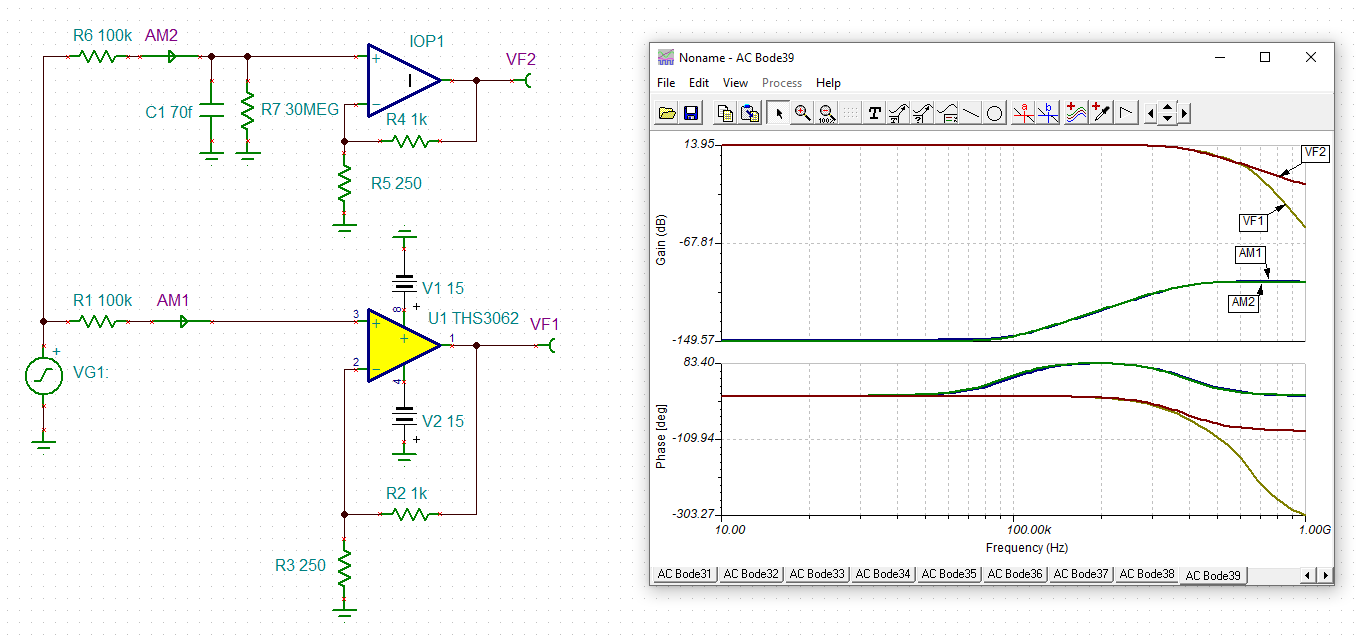

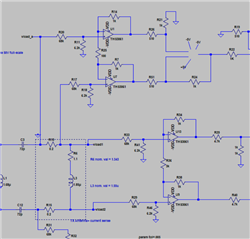

我将 THS3062配置为仪表运算放大器、如下所示:

电流 ns+和电流 ns-输入是13.56MHz 下的~2Vp 正弦波。 我希望这些信号在引脚3和5处具有稍小的同相版本。 相反、我看到看起来是0.45V 直流信号。 可能发生什么事了? 引脚3和5是高阻抗输入。 我已经验证了电路板上的电源、布局、组件值、组装选项等。 我被骗了。 是否有任何关于可能发生的情况的建议?

电路仿真效果良好。

谢谢、

豪尔赫

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我将 THS3062配置为仪表运算放大器、如下所示:

电流 ns+和电流 ns-输入是13.56MHz 下的~2Vp 正弦波。 我希望这些信号在引脚3和5处具有稍小的同相版本。 相反、我看到看起来是0.45V 直流信号。 可能发生什么事了? 引脚3和5是高阻抗输入。 我已经验证了电路板上的电源、布局、组件值、组装选项等。 我被骗了。 是否有任何关于可能发生的情况的建议?

电路仿真效果良好。

谢谢、

豪尔赫

您好、Michael、谢谢。

我尝试了它,它有所改进,但它仍然不是我所期望的。 2Vp 信号降至约880mV。 ‘ll、考虑到运算放大器的输入电容、这可能是正确的–I μ F 必须查看–但它看起来太大了。

因此、如果偏置电流为6uA (数据表中的典型值)、且电阻为68kohm、则失调 电压应为0.4V。 因此、仅偏置电流不应成为同相信号处输入信号不符合我预期的原因。 它们会向输入信号提供偏移。

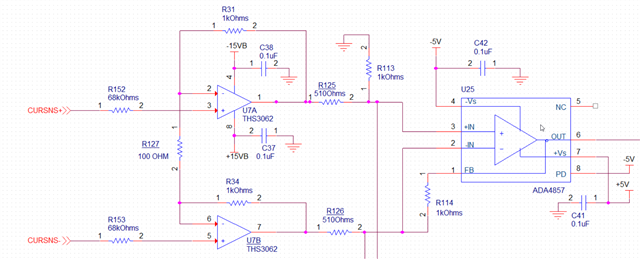

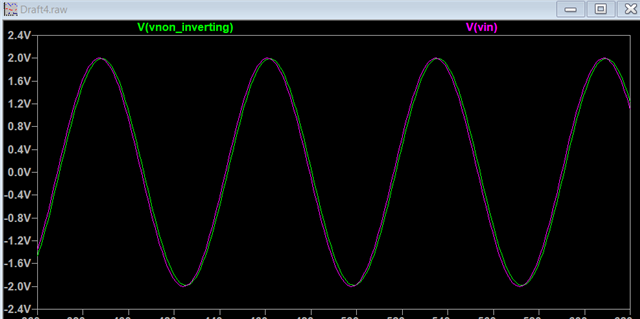

如果我将运算放大器的该输入建模为如下所示:

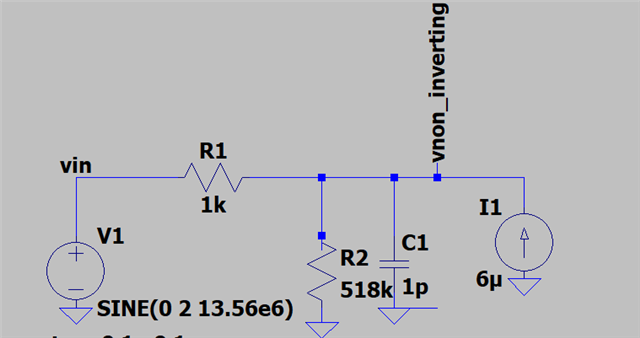

在串联1k 电阻的情况下、我仍然得到:

因此,我在电路板上测量的880mV 并不是很正确。

这很奇怪。 这些运算放大器也变得很热–很显然、论坛上的其他人也注意到了这一点!

再次感谢您的参与。 我觉得68k 太多了、但可能还有其他东西。

豪尔赫

因此、是的、在每个电流约为10mA 且电源电压为30V 的情况下、静态功率约为600mW、您会感到这种情况。

因此、您确实具有相当多的差分增益(21)-无论这些2Vpp 输入是否相位差、您都将过驱输出

另一种长时间触发机制是 DIFF I/O 级有时会出现 CM 稳定性问题。 通常情况下、RF 过高的 CFA 不是如此、但测试将100欧姆增益元件拆分为两个50欧姆元件、并通过假设10nF 电容器将其中心点接地。 这对所需的差分信号是不可见的、但在较高频率下将 CM 增益提高了相当多的值。

昨天我并没有真正填补一些空白、但如果您看到本质上是一个奇怪的输入阻抗(您看到的衰减必须是这种情况)、则可能是由于某个器件未在其线性区域中运行。 如果输出拆裂到电源轨中、则其中的一些器件会反馈以改变输入级特性。 如果是按 CM 振荡的器件、则同样可以通过热机制或操作点问题返回输入级。 如果部件有这些问题与您所寻找的内容重叠、则所有赌注都将关闭-而不是这样、只是猜测此时。

您好、Jorge、

奇怪的是你是如何折磨这个运算放大器的

THS3062是一款300MHz 电流 µs 运算放大器、压摆率为7000V/μ s。 您不能将此类占位符视为标准1MHz 运算放大器。 对于40µA μ A 输入偏置电流、68k 输入电阻过高。 这看起来是完全荒谬的。 并且、您会将过高的输入信号和过高的增益组合在一起、严重地过度驱动输出。 这将不起作用、而直流偏移电压漂移正是您在以这种方式对 HF-OPAMP 进行纹理时所习惯看到的。

Kai

尊敬的 Kai:

我的荒谬电路在仿真中表现得非常好–我不知道该运算放大器的模型对实际器件的保真度如此低。

我同意68K 为高电平–但偏置电流不应成为问题。 它们应 在 同相输入端以及68K 和40uA 时添加一个直流失调电压、相当于2V 的失调电压、这完全在运算放大器的共模电压范围内。 我正在使用+/-15V 电源轨为运算放大器供电。

频率响应是一个不同的问题,因为在13.56MHz 时为68K (实际上为68k||518K)和1pF,因此同相输入端的衰减为0.12。 这是我的错。 它仍然没有解释为什么当我将电阻器更改为1k 时,运算放大器的输入端不会得到预期的 Vin*.90。

驱动运算放大器太硬……不确定您所说的内容。 每个运算放大器都看到2Vp 正弦波。 实际上、 如果我回忆一下该运算放大器的规格、我应该能够驱动高达8或9伏的电压。 在配置为差分仪表放大器时,我用该电路的增益放大的信号约为50mV。 因此总体增益较大。 但是、请照亮我。 您建议如何放大0.2欧姆电阻器上的电压差?

我感谢你的帮助。 但是,在将来,我会建议您先了解我要做的事情,然后再说一些荒谬的事情。 最终可能仍然是荒谬的,但我真的不需要你告诉我。 您可以解释为什么它不起作用、并在没有该评论的情况下为我提供一些指导。

豪尔赫

您好、Jorge、

绝对是个好地方 我同意 Michaels 的意见、即如果两半之间的相位延迟、您可能会导致输出过驱、进而导致非线性行为、进而导致衰减信号。 使用1k 串联电阻器时、每个单独输出和差分输出在示波器上看起来是什么样子的?

您的示波器探头的电容是多少?

Michael 提出的另一个问题是、如果您可以为 Rg 使用两个50欧姆电阻器、并使用电容将中心点接地、则会提高 CM 增益。

最后、我想知道如果您输入差分信号、放大器会做什么。 您必须将每半部分的信号降低到大约1Vpp。 这是否会在同相引脚上产生衰减信号?

谢谢、

Samir

嗨、Jorge、

我们将通过此时显然是硬件测试来解决您的直接问题。 但我再次查看了您的完整原理图(从本质上讲、在大差分信号上拔出一个小信号、将其向上拉、然后耗尽单端信号)、您或许应该知道另一种解决方案。

我们在 AWG 信号路径中使用了这些器件、但如果您重新设计、可能会对此感兴趣。

THS3215可能足够了(THS3217速度更快)、并且包含一个增益固定为2的固定增益前端差分放大器。 如果需要、可以设置第二级 OPS、以使该差分残留物具有相当高的增益(类似于 THS3062的 CFA)。 它不是那么高的电源电压、但我无法告诉您确实需要+/-15V 电源。

您好、Jorge、

如果您有一个具有 JFET 或 CMOS 输入级的运算放大器、则源电阻(R152、R153)不会发挥太大的作用。 输入偏置电流很低、输入电容将与源电阻结合使用、充当低通滤波器。

但在这里、您有一个具有 BJT 的输入级、该输入级需要相关的静态和动态(!) 以确保基极电流正常运行。 如果电源电阻过高、您将调节输入级并破坏 HF 工作点。

THS3062针对从+input 到信号接地端的阻抗小于75R 进行了优化。 电气特性中显示的所有数据都已在这个测试条件下获得。 您也可以从最大输入偏置电流规格中看到这一点:40µA x 75R = 3mV。 该范围与 THS3062的4.5mV 最大输入失调电压相同。 您可能可以将源阻抗增加10倍、从而产生大约数百欧姆的电阻。 但是、您还可以在一年后从68k 开始。

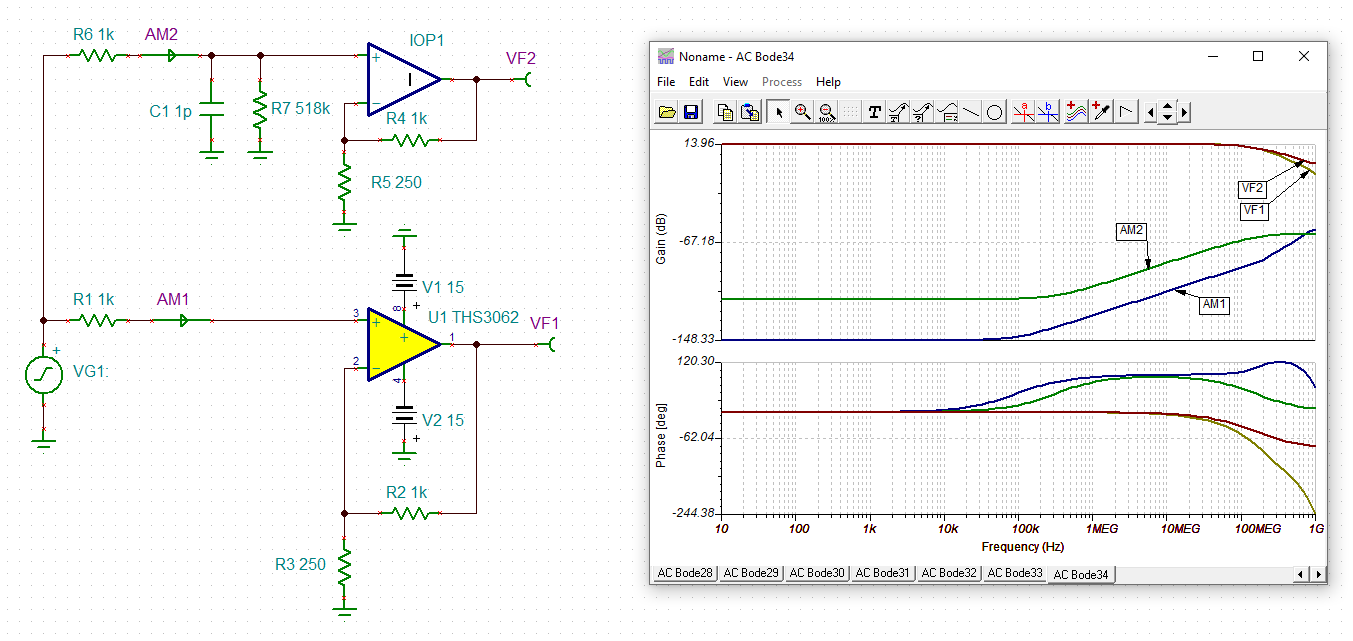

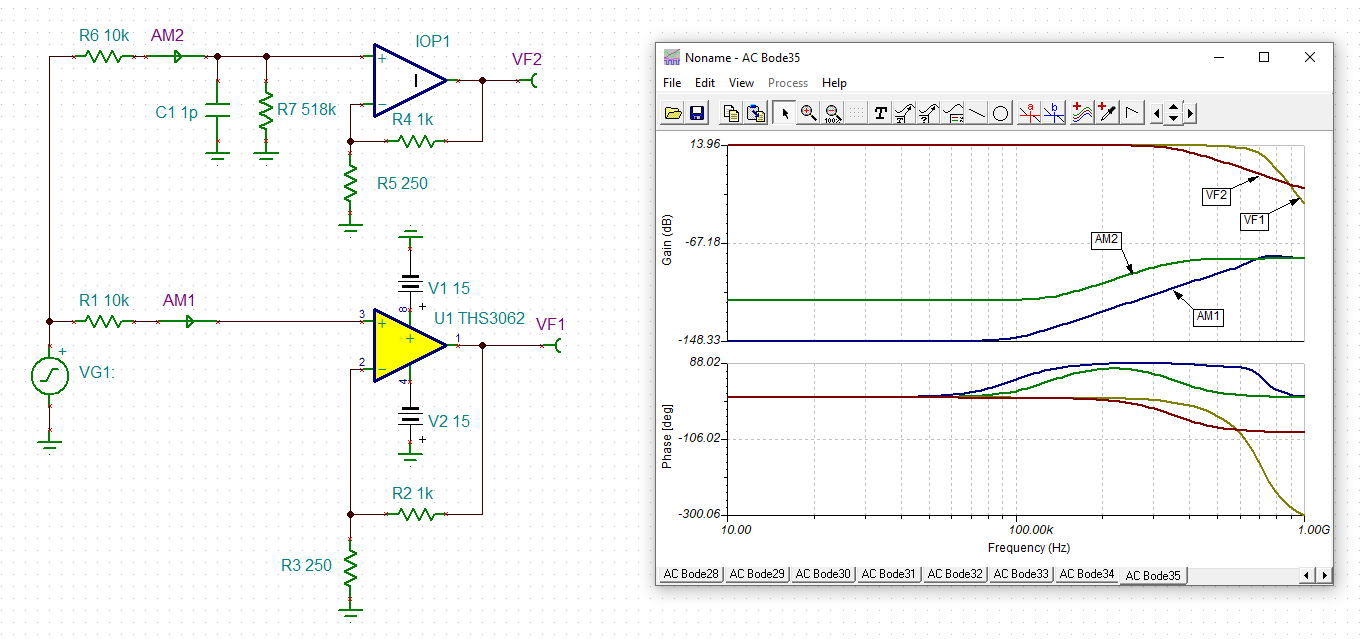

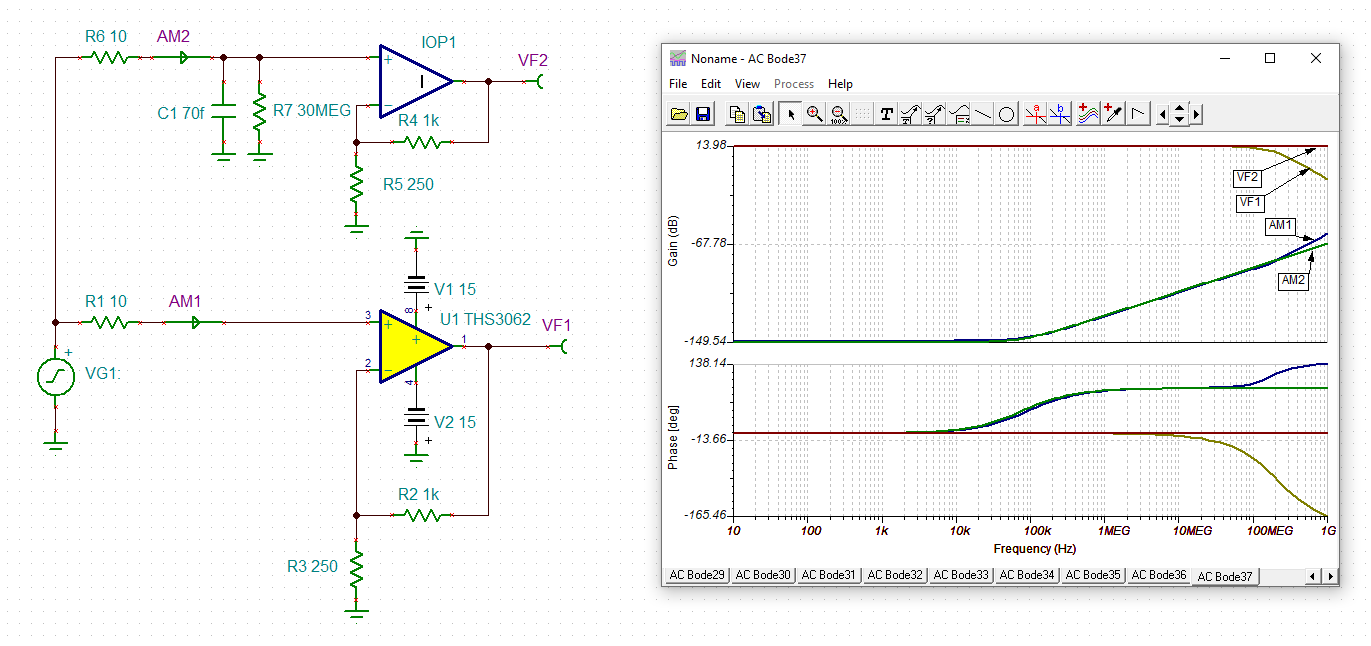

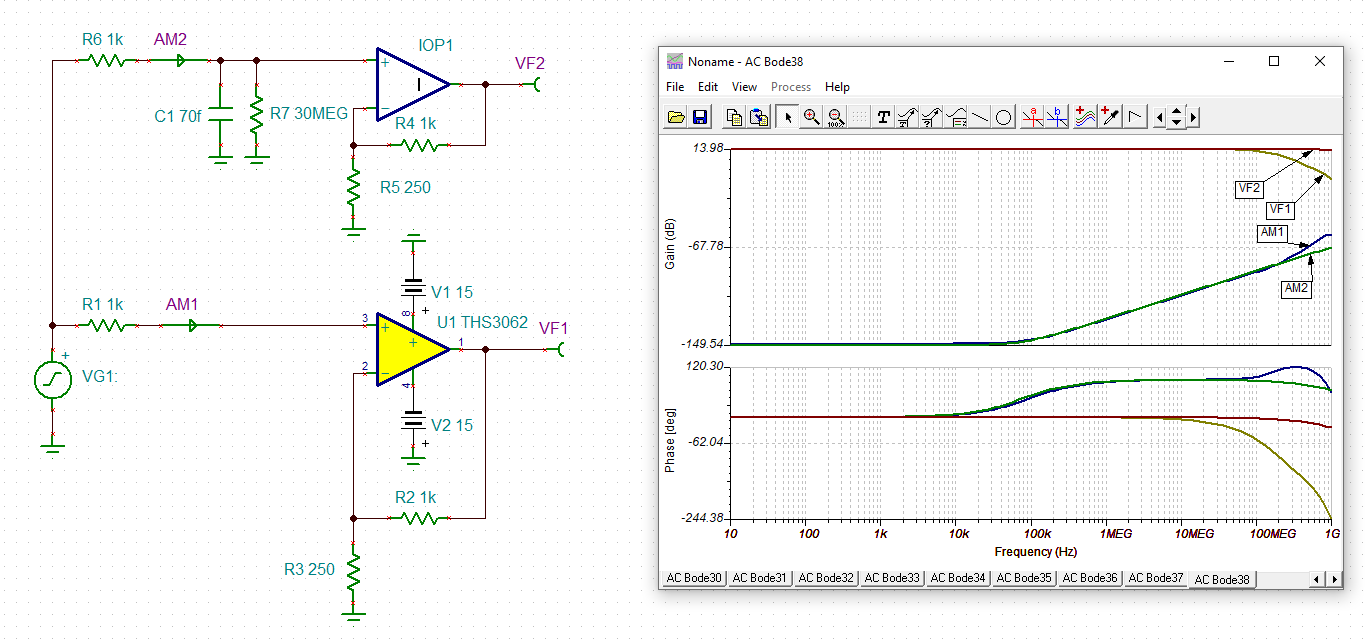

遗憾的是、THS3062的 SPICE 模型并不理想。 输入电容和输入电阻建模不当、我认为动态输入电流建模也不正确。 请参阅以下仿真、其中我将 THS3062与由 THS3062的指定输入电容和输入电阻所添加的理想运算放大器进行比较:

70fF 和30M 提供比1pF 和518k 更好的适配:

e2e.ti.com/.../jorge_5F00_ths3062.TSC

因此、THS3062的输入级未正确建模、仿真将不会向您展示68k 源电阻的实际情况!

话虽如此、在具有低源阻抗的标准电路中、该模型运行良好

Kai

再次感谢你的帮助。

这种模式离得太远,这是令人遗憾的。 我对整个电路进行了仿真并运行良好,我的预期是,硬件需要进行一些微调才能使其正常工作 ,而不是“不起作用”。

我没有设置为68K -我只是想使用高阻抗来避免加载被测电路- 1k 或更低可能可以正常工作-我只需要处理它。

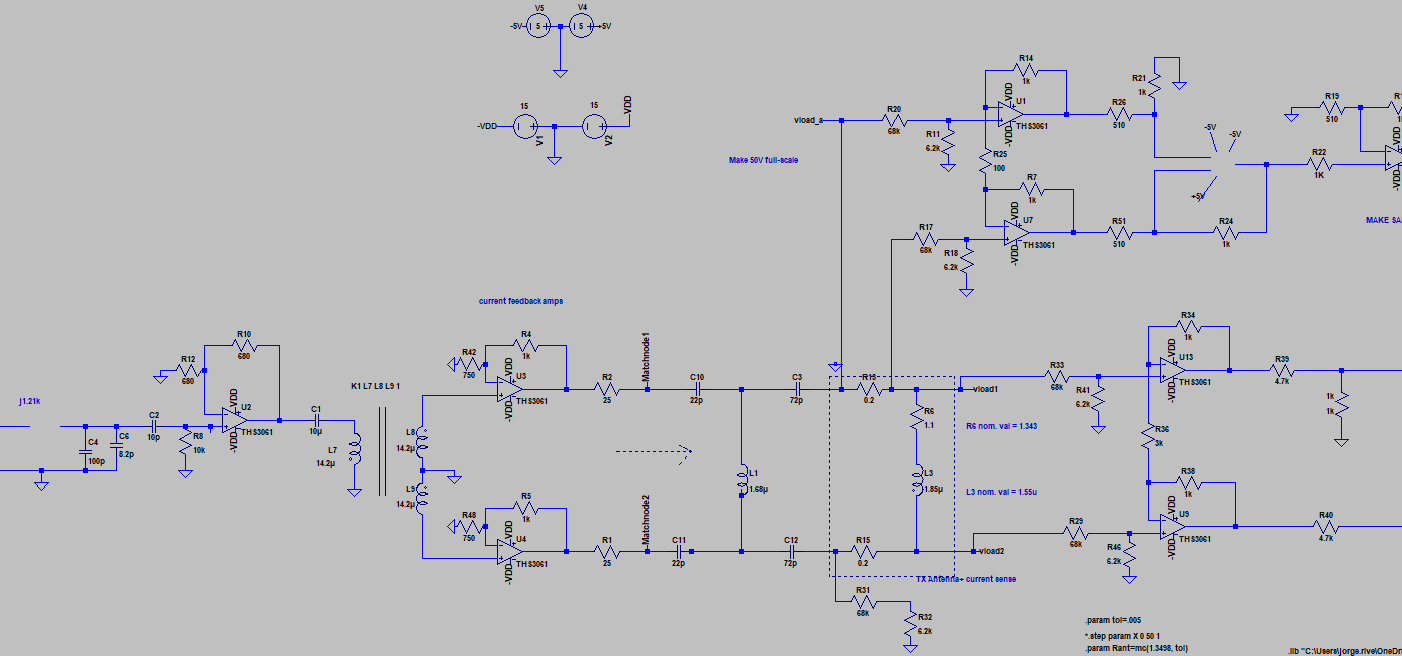

我共享的电路部分是放大感测电阻两端压降的部分。 附件是完整的电路(虽然它在 LTSpice 中,但我也包括了网表)。 我从13.56MHz 振荡器启动、滤除基频、并将信号转换为平衡信号以差动驱动负载(线圈–类似于 NFC 天线)。 然后、我会监控负载上的电流和压降、以确定是否存在金属或电容物体时硬币的增量阻抗变化。

感应电阻器上的差分电压非常小、因此仪表放大器中的增益较大。 在电压侧、在负载上、差分电压较大、因此信号调节变化不太严格。 检测电阻器两端的电压(电流)和在负载上感应到的电压随后馈送到2通道同步采样 ADC (40MHz 时)、以便负载的阻抗(或 Δ 阻抗)可以是 calculated.e2e.ti.com/.../oscillator_5F00_PA_5F00_balun_5F00_match_5F00_to_5F00_1_5F00_1_2B00_j158.zip

豪尔赫、

当您进一步解释这一点时、我想知道为什么您在前端使用非常高的压摆率双 CFA

就像一个猜测一样、我本来应该使用两个 OPA838、在这个数据表中、我在应用文本中谈论 CM 环路振荡。 不适用于您的电路、但会适用于 OPA838 -我实际上已将 OPA838应用于 Google 项目、

因此请记住、考虑到 THS3062的 V+输入已经非常高的阻抗、您无需使用外部(有噪声)电阻器升高。 串联。

您好、Michael、

当我开始研究这个问题时、我开始研究 BW、我认为是转换率问题。 我首先使用高速电压反馈运算放大器、但观察到的失真和非线性会驱使我使用 CF 类型。

是的、我可以将输入电阻器的0欧姆跳线连接到运算放大器的同相输入端。 他们在那里寻求隔离、因为我知道我在启动电路板时会重新访问他们的值。 但是、我需要一些电阻、因为我需要将信号降低到运算放大器的 CM 范围。 输入端的信号可高达50V。 (运算放大器要求高转换率的另一个原因)。

您是否能够看到我在 对 Kai 的响应中上传的电路?

您好、Jorge、

[引用 userid="473685" URL"~/support/amplifiers-group/amplifiers/f/amplifiers-forum/1014811/ths3062-strange-behavior-from-opamp-at-non-inverting-input/3753229 #3753229"]模型远不及这一点让人感到遗憾。是的、这有时很烦人。 但比什么都好。

[引用 userid="473685" URL"~/support/amplifiers-group/amplifiers/f/amplifiers-forum/1014811/ths3062-strange-behavior-from-opamp-at-non-inverting-input/3753229 #3753229"]我没有设置为68K -我只是想使用高阻抗来避免加载被测电路- 1k 或更低的电阻可以正常工作-我只需要处理它。[/quote是的、我理解、您希望将天线与 OPAMP 的输入阻抗隔离。 我也会这样做。

[引用 userid="473685" URL"~/support/amplifiers-group/amplifiers/f/amplifiers-forum/1014811/ths3062-strange-behavior-from-opamp-at-non-inverting-input/3753238 #3753238">您能解释一下我在使用 AM1和 AM2信号时看到的内容吗? 例如、对于 R6 = 100k、C1和 R7分别为70fF 和30Meg 的情况、为什么不是-0.0289? 在直流时,增益图不应仅反映分频器,即20*log10 (30/(30+/0.1))? [/报价]AM1和 AM2信号以输入信号 VG1为基准、并形成 AM1rms / VG1rms 的比率。 如果 VG1rms=1V 且在直流时 AM1为1V/30.1Meg = 33.22591nArms、则这意味着"增益"为20 x log (33.22591n/1)=-149.57dB。 "log"是这里的以10为底的对数。

以下是 LTSpice 原理图的一个片段:

Kai

您好、Jorge、

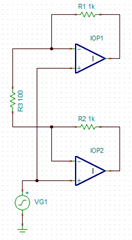

在下面的电路中、当对两个放大器的输入施加相同的信号时、100欧姆电阻器的两侧存在0V 差值。 因此、输入信号(VG)在两个放大器的输出中均得以再现...因此信号增益为1。 您会注意到、G=1V/V 配置的相位裕度比增益配置的高。

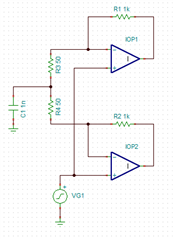

现在、如果您使用下面的电路、例如、在中频时、电路的工作方式与上述相同、 然而、在高频下(在稳定性很重要的放大器交叉区域附近)、您具有到 GND 的低阻抗、以便对每个单独的放大器反馈环路进行去耦、并导致一个更高的噪声增益电路。 现在、电流反馈放大器(CFB)的稳定性基于反馈电阻的值、但存在次级噪声增益效应。 A CFB 的反馈因子= (RF + Ri *噪声增益)。 有关 CFB 补偿的更多信息、请观看此视频。

通过增加高频噪声增益、您可以提高相位裕度、然后提高稳定性。 希望这有助于/

那么、Jorge、看看 Kai 从 LTSpice 输入的内容、这里发生了很多事情、但您的问题是否与这两个阶段相关?

这接近于您最初输入的值、但它确实显示了 V+节点的衰减? 那么、这里到底讨论了什么呢?

此外、我一直假设您具有这种内置和探测功能。 我的很多评论都暗示了可能出现异常操作、从而给出了奇怪的探测结果-这显然意味着检查振荡? 这些电流可能会表现为过度的电源电流消耗、当然、在频谱分析仪中、它会超出您的预期应用范围。 不确定是否要这样做、但我使用小型 MAG 导线环作为 A 规格中的非侵入式探头

是的、这些阶段。 仿真正常...电路板不工作。 当电路板上的探测点与 我在仿真中看到的预期水平不匹配时、我开始了这个线程。

未测量振荡。 只是值错误。 但是,正如您最初指出的,主要是由于68k 欧姆。 我需要返回并验证运算放大器中具有~1k 源阻抗的节点电压和信号、但我需要更改许多值、以便先将所有值恢复到运算放大器输入端的"正确"电压电平。 我还必须更改天线、因此我要将其重新匹配到50欧姆的源。 正如 最初设计的那样 ,“vloada”上的电压在50V 范围内……

您好、Jorge、

[引用 userid="473685" URL"~/support/amplifiers-group/amplifiers/f/amplifiers-forum/1014811/ths3062-strange-behavior-from-opamp-at-non-inverting-input/3753987 #3753987">看起来有些符号没有通过..... 请告诉我您是否需要这些文件--我以为我将它们包含在 zip 文件中,但也许我无意中将它们关闭这是我的错。 我的 LTSpice 不知道这些 ADAS ...

Kai