Other Parts Discussed in Thread: THS3062, THS3215, THS3217, OPA838

主题中讨论的其他器件: THS3215、 THS3217、 OPA838

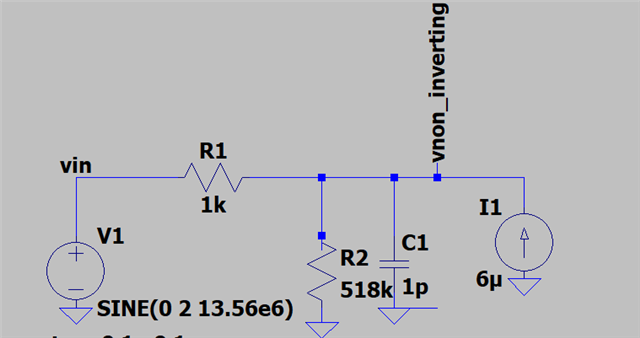

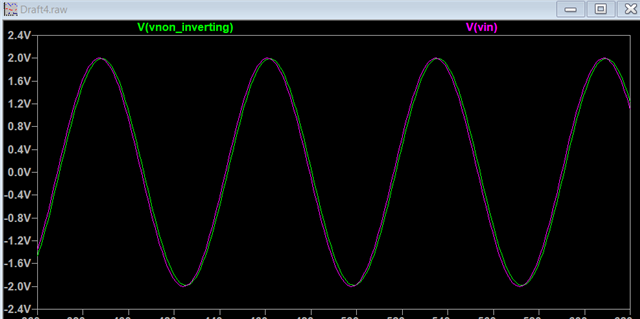

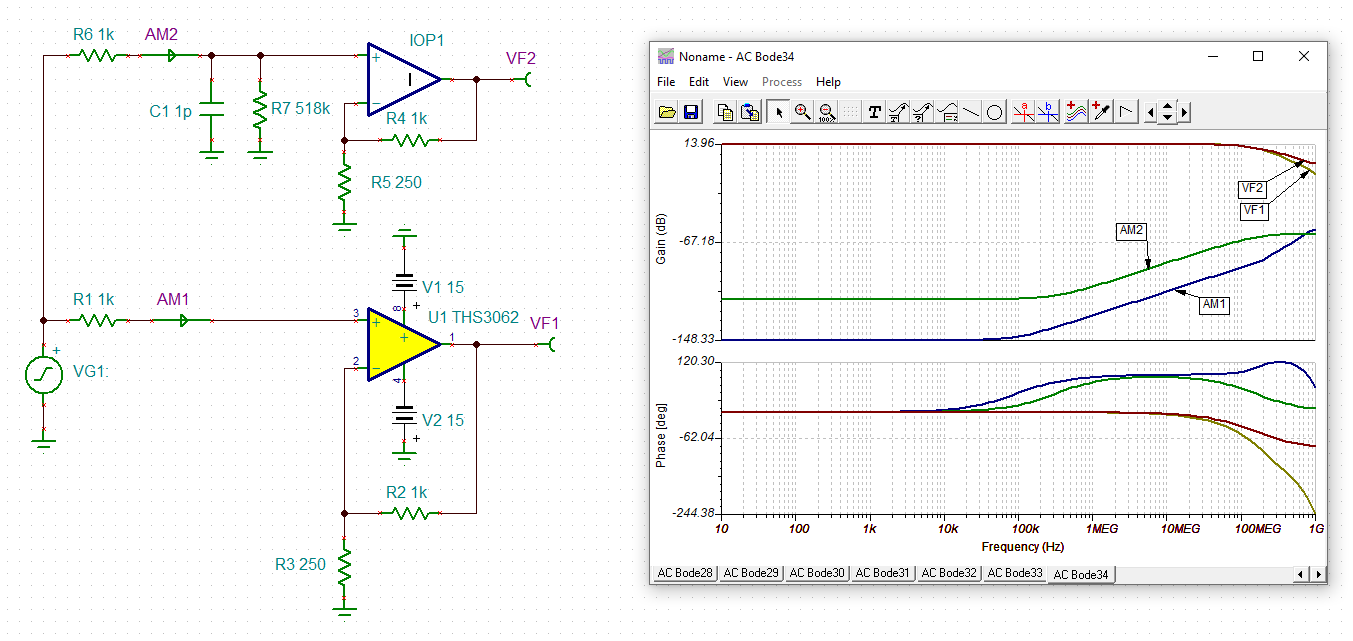

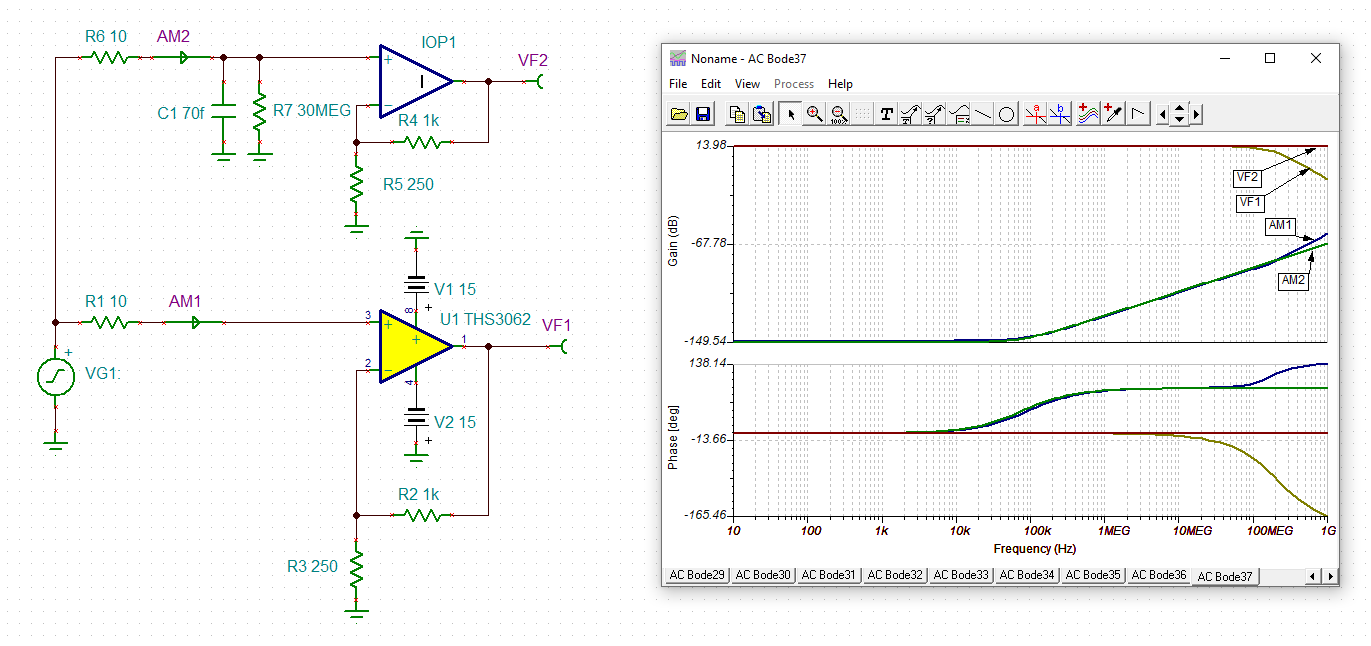

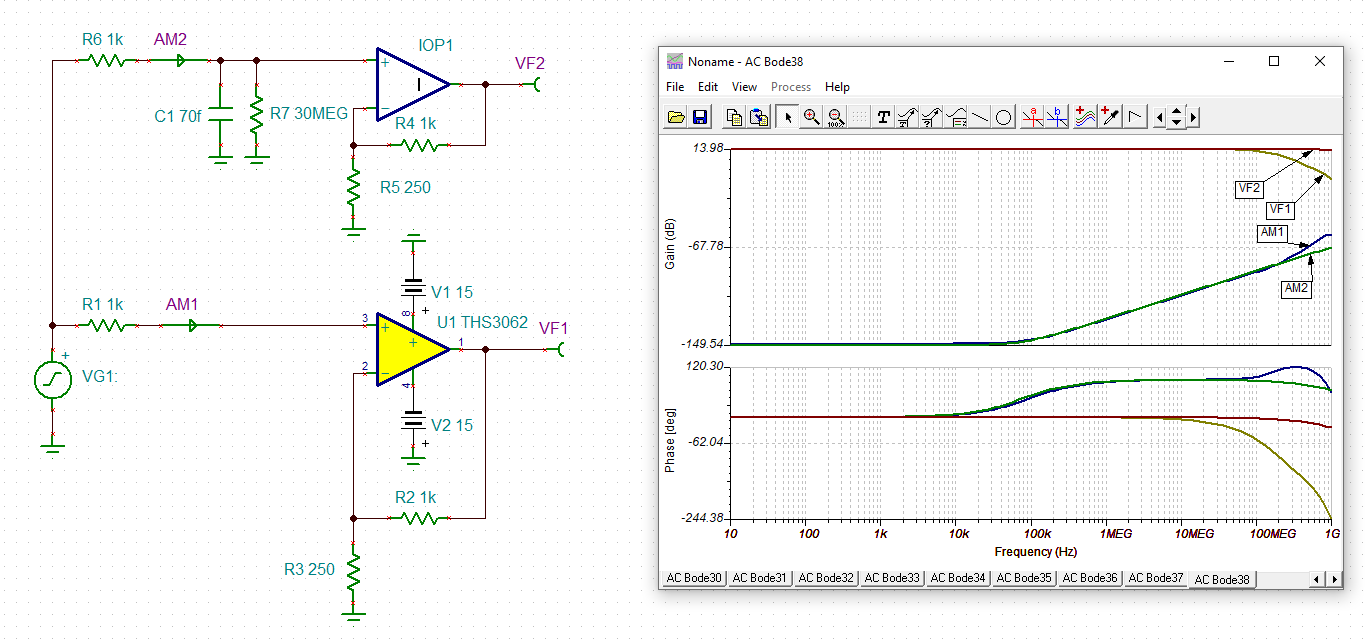

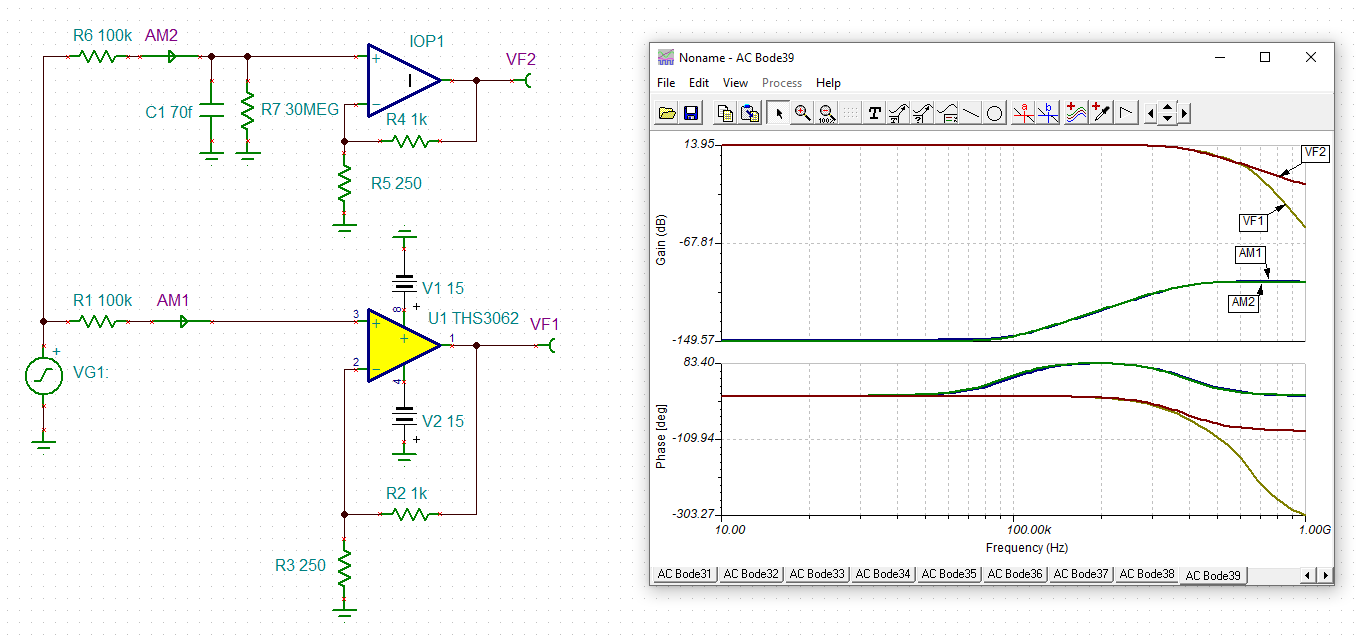

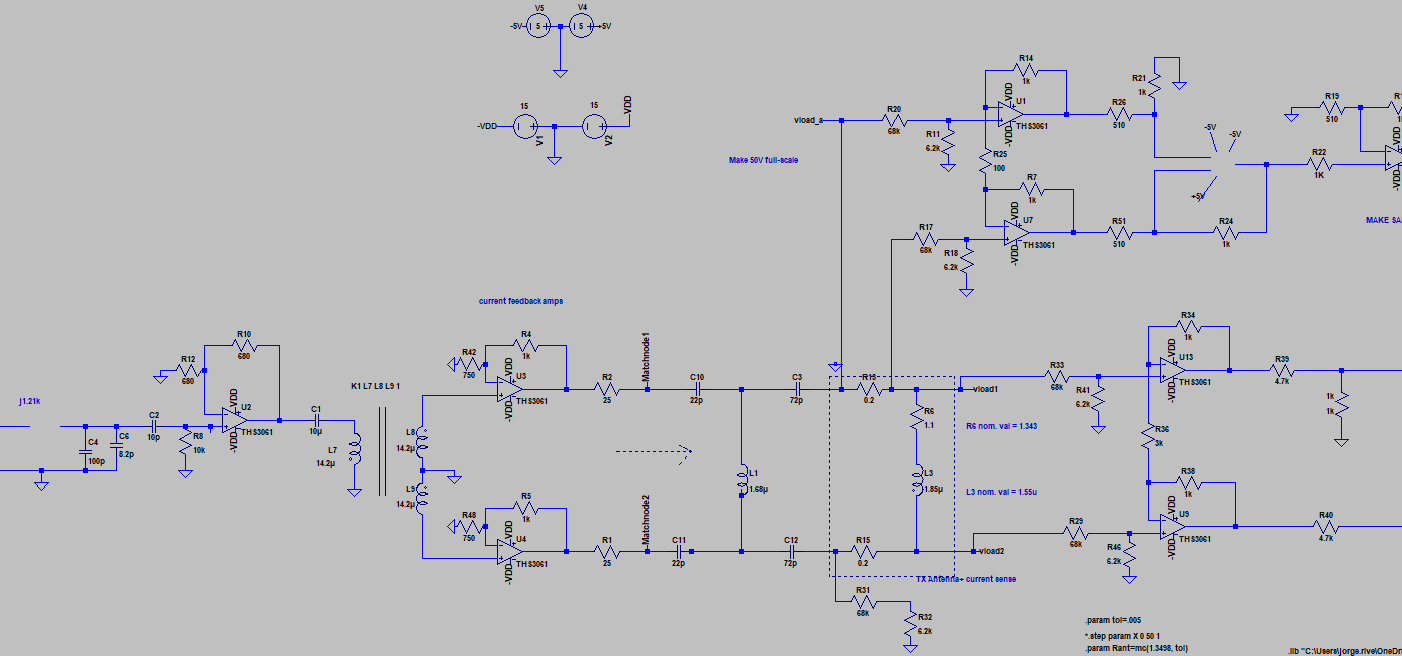

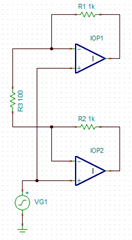

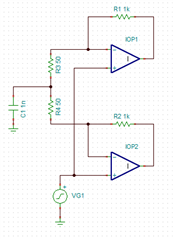

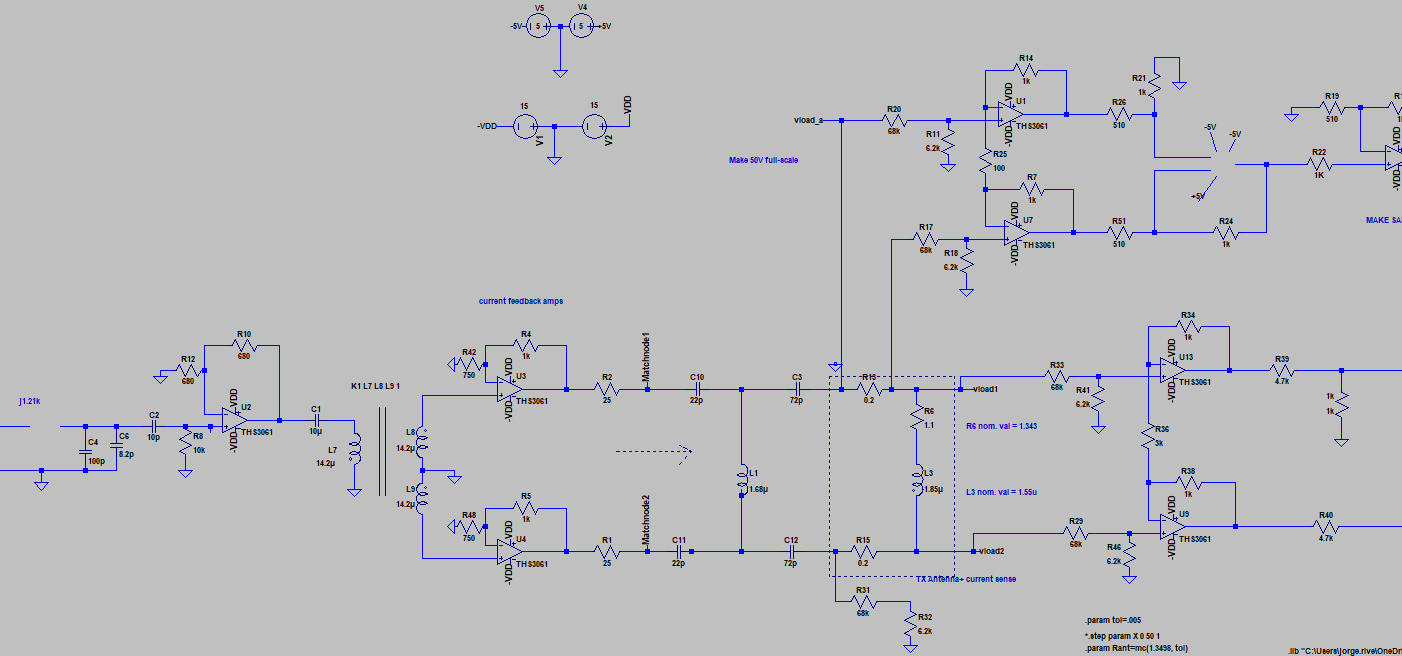

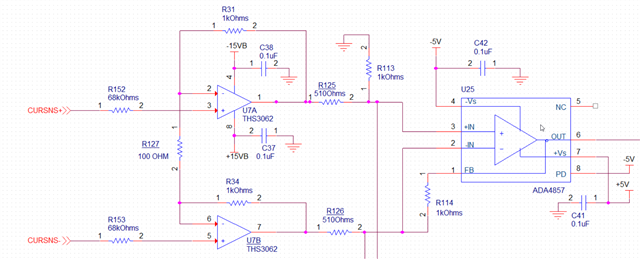

我将 THS3062配置为仪表运算放大器、如下所示:

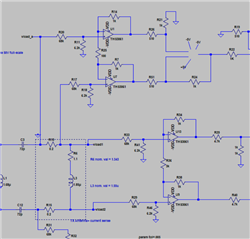

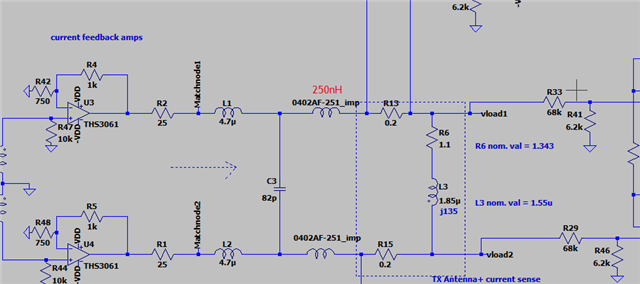

电流 ns+和电流 ns-输入是13.56MHz 下的~2Vp 正弦波。 我希望这些信号在引脚3和5处具有稍小的同相版本。 相反、我看到看起来是0.45V 直流信号。 可能发生什么事了? 引脚3和5是高阻抗输入。 我已经验证了电路板上的电源、布局、组件值、组装选项等。 我被骗了。 是否有任何关于可能发生的情况的建议?

电路仿真效果良好。

谢谢、

豪尔赫