您好、TI 专家

我们在 AM263x SDK V8.2中遇到了多 CAN 消息的 MCAN RX ISR 延迟问题

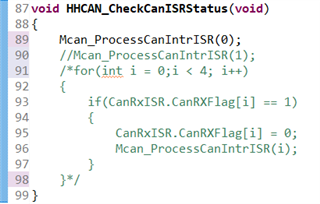

(1)当我们仅为 用 1ms 时间触发任务的 CAN0启用 MCAN_ProcessCanIntraISR (0)时

当接收到200ms 周期消息时、MCAN_ProcessCanIntrISR (0)触发器有延迟问题(200~1000ms)

(2) CAN 总线负载(~4%)如下 :

CAN0发送的 CAN ID:0x228和0x504 (CAN 工具中显示 RX)

CAN0接收的其它 CAN ID (TX 显示在 CAN 工具中)、

是否有任何关于 MCAN_ProcessCanIntraISR 用于多 CAN 消息的建议?

BR

Jay