主题中讨论的其他器件: TM4C1294NCPDT、 TPS22969

您好、香榭丽舍

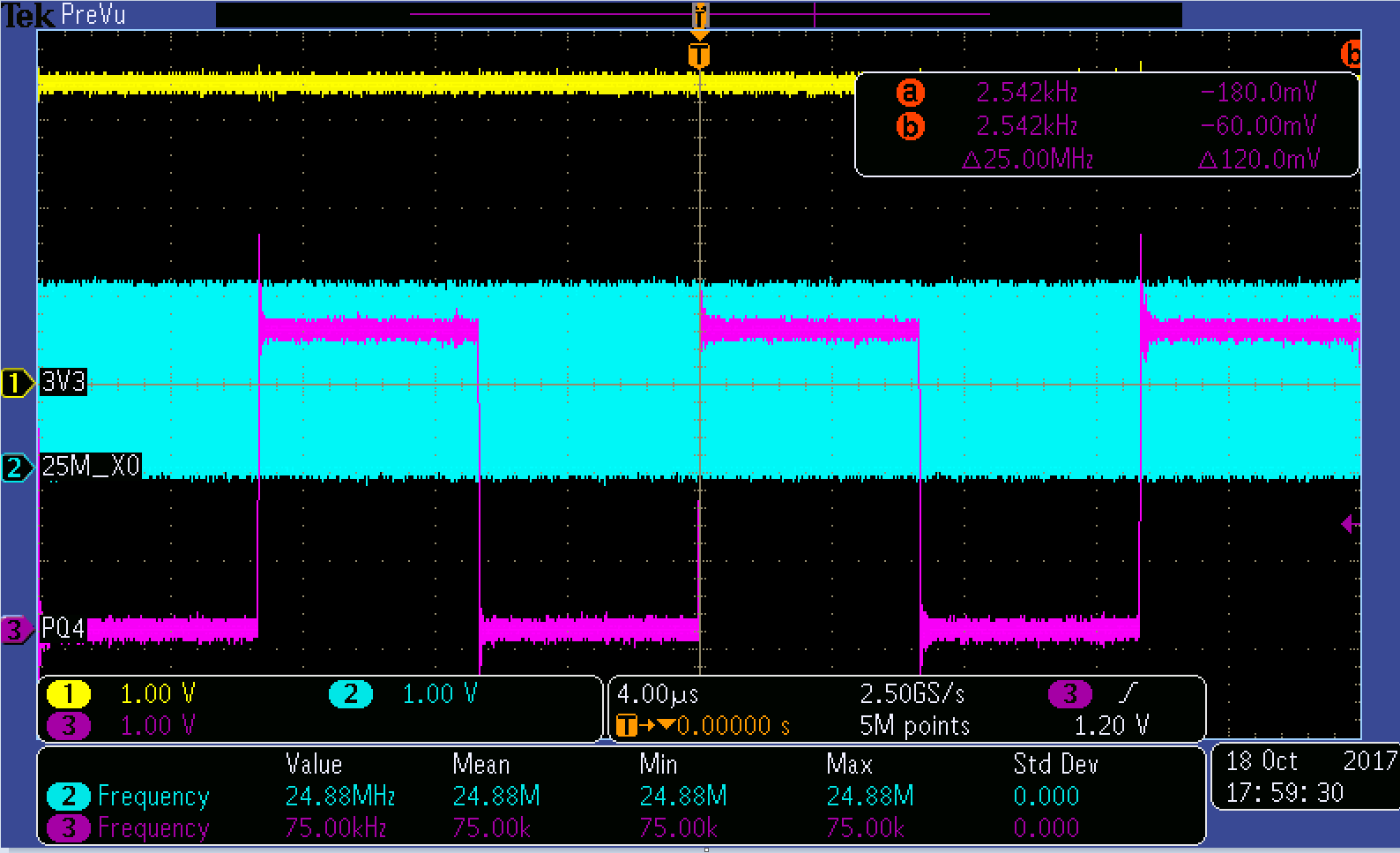

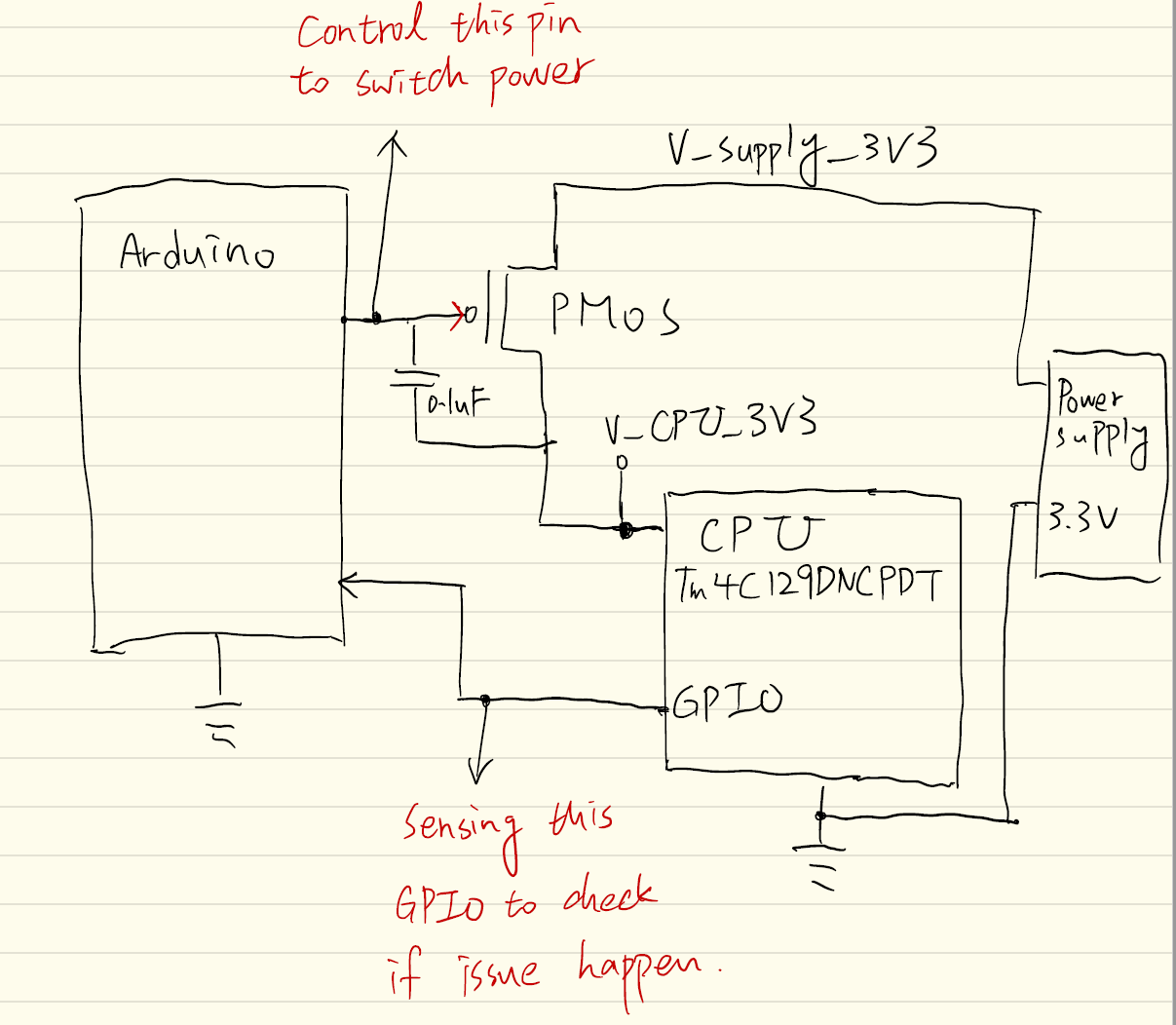

我的客户设置了打开/关闭 M4的测试程序。 上电周期为1。 它们将 PQ4配置为 DIVSCLK 输出。 它们监控 PQ4时钟。 通常情况下、PQ4时钟将为1.2MHz、因为 SYSCLK 为120MHz 并且 DIVSCLK = 99

客户测试程序如下所示。

1.使用 Arduino 执行关机测试

2.当 TM4C129DNCPDT V_3V3上升时、Arduino 开始计数65ms

3. 65ms 后,Arduino 将检测由 FW 分配的 GPIO (如果 GPIO 仍处于低电平)

状态、Arduino 将使 V_3V3等待调试。

->因为如果 SYSCLK 为120MHz、GPIO 将在65ms 之前拉高。 如果 GPIO 在65ms 后仍然为低电平、则意味着 SYSCLK 被改变

4. 如果 GPIO 处于高电平状态、Arduino 将关闭 V_3V3、并在1秒内再次执行步骤2~步骤3、直到问题发生。

GPIO PQ4用于检测内部系统时钟

。

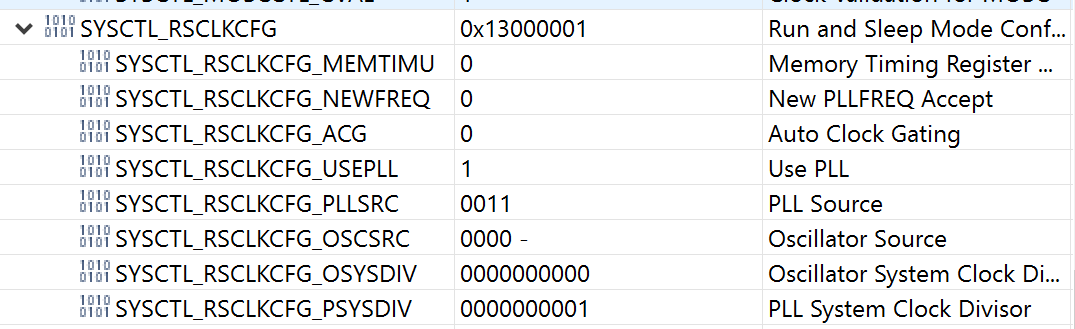

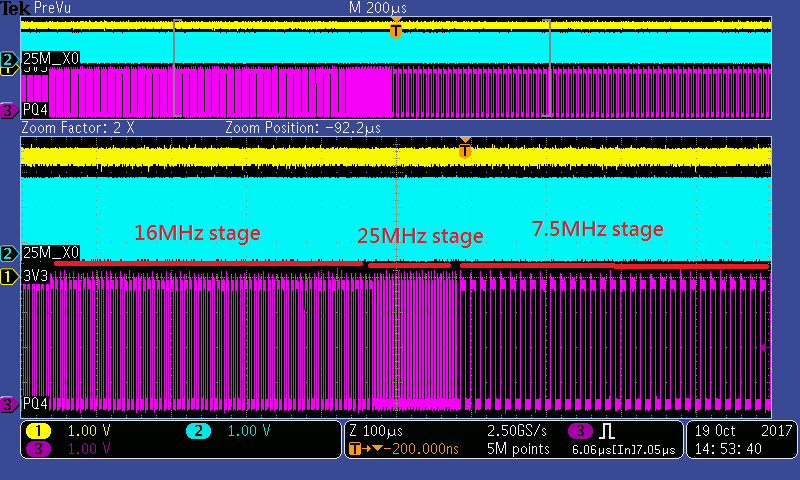

发生问题时、PQ4的频率为75kHz、这意味着 SYSCLK 为7.5Mhz。 Fvco=240、7.5Mhz = 240/32。 看起来像 PSYSDIV =32。 我连接了 ICDI 以检查内部 SYSCTL_RSCLKCFG 和 STSCLT_PLLFREQ0/Q1。 设置如下所示。 但是、PSYSDIV 为0x1。 我还检查仍然生成25MHz 时钟的 XTAL。

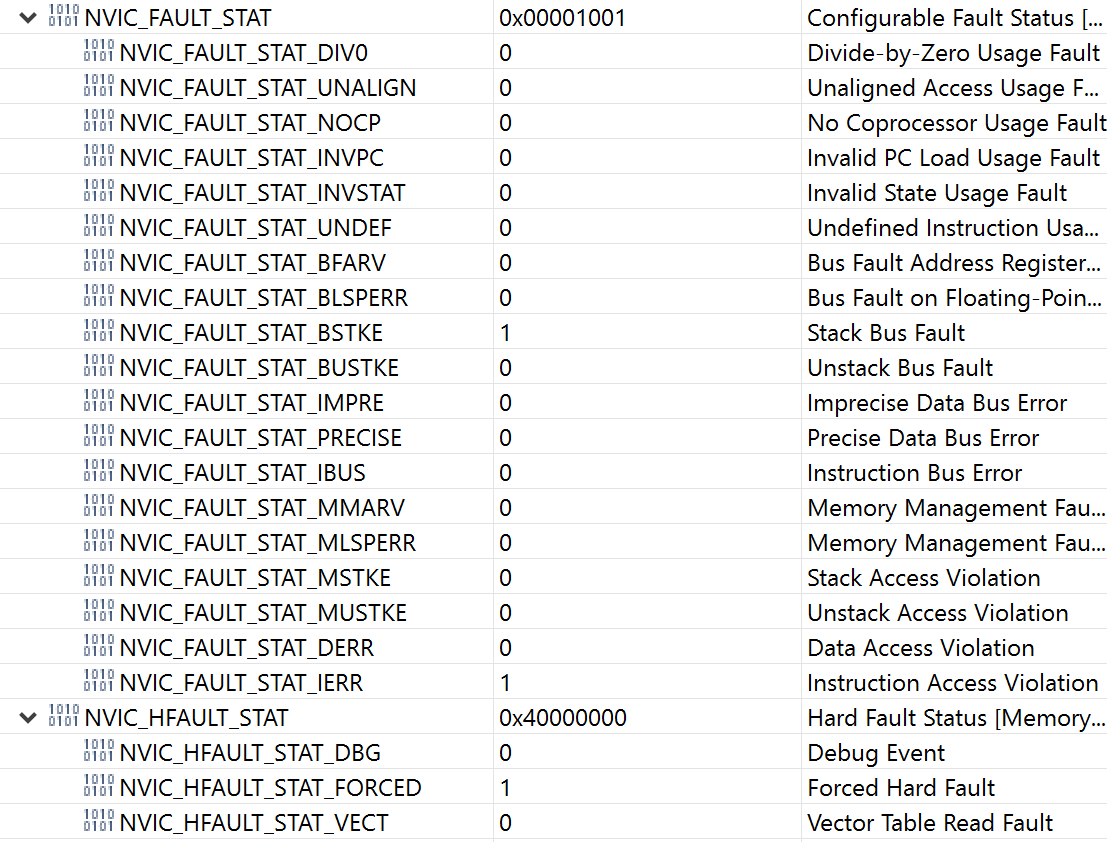

另一件事是、当我重写 PSYDIV = 2且 PQ4输出频率变为0.6Mhz 时。 然后我重新写入 PSYDIV=1、PQ4时钟频率变为1.2MHz。 看起来系统没有将正确的值加载到 PSYDIV 中。 当我们查看勘误表时、我们发现提到 PSYDIV 值的 SYSCTL#22可能不会加载到物理分频器中、从而导致系统时钟被2分频。

我们认为这与此勘误表相关。 请在这方面提供帮助? 谢谢!

客户还想知道 TM4C1294NCPDT 和 TM4C129DNCPDT 之间的区别是什么。 他们以前在 TM4C129DNCDPT 上遇到 SYSCLK 问题、并尝试在使用 TM4C1294NCPDT 的 Launchpad 上重复出现问题。 但是、当他们将 IC 更改为 TM4C129DNCPDT 时、他们不能重复出现的问题。 谢谢!

寄存器设置

PQ4输出波形