您好!

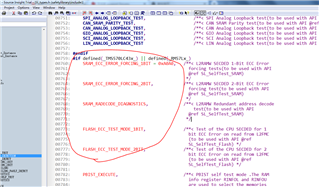

在仔细阅读诊断库代码之后、我没有发现 SRAM/FALSH 具有针对 RM57Lx 器件的故障注入测试类型。

您能帮助检查一下吗? 如果真的不是、如何为他们执行故障注入?

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在仔细阅读诊断库代码之后、我没有发现 SRAM/FALSH 具有针对 RM57Lx 器件的故障注入测试类型。

您能帮助检查一下吗? 如果真的不是、如何为他们执行故障注入?

谢谢。

您好、QJ:

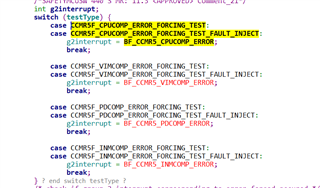

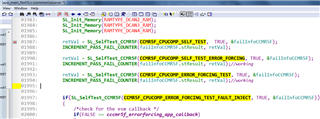

不仅 SRAM/闪存、CCMR5F 模块还具有同样的问题。

XXX_ERROR_FORCING_TEST 和 XXX_ERROR_FORCING_TEST_FAULT_INject 之间的区别是什么?

您 强调了它们是相同的、对于故障注入而言也是相同的。 为什么不将它们合并到一个测试中、因为它们是相同的测试?

对于 示例代码中的以下4个 CCMR5F_CPUCOMP 测试、您只需从回调函数获得 xxx_Inject 测试的测试结果、并从

其他3个测试的故障信息结构。

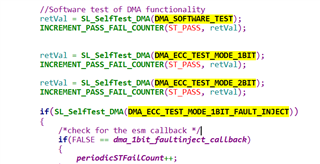

DMA 与 CCMR5F_CPUCOMP 相同。

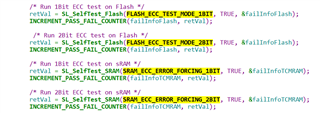

此外、针对 SRAM/闪存的所有错误强制测试通过 failinfo 结构给出测试结果、而不是 ESM 回调函数。

那么、您能强调 XXX_ERROR_FORCING_TEST 和 XXX_ERROR_FORCING_TEST_FAULT_INject 之间的区别吗?

XXX_ERROR_FORCING_TEST 和 XXX_ERROR_FORCING_TEST_FAULT_INject 之间的区别是什么?

您 强调了它们是相同的、对于故障注入而言也是相同的。 为什么不将它们合并到一个测试中、因为它们是相同的测试?

[/报价]这两个选项的测试机制相同。 MKEY4 = 0x9。

但是、一个测试处于轮询模式、另一个测试处于中断模式(回调)。

谢谢 QJ。

如您所述、这两个测试选项都用于注入故障。

首先、当我们使用 XXX_ERROR_FORCINF_TEST 作为测试类型时、测试将注入人工的1位/2位 ECC 故障。

如果能够纠正故障、则结构中的结果将为通过、如果无法纠正故障、则结果将为失败。

此时、ESM 中断可被启用或者解除以响应可校正/不可校正的故障。 对吧?

其次、如果我们使用 XXX_ERROR_强制 执行_TEST_FAULT_INject、这意味着将注入不可纠正的故障、

结构的结果必须失败并且 ESM 中断必须被触发并且如果 ESM 中断被提前启用的话、必须调用回调函数。 对吧?

首先,当我们使用 XXX_ERROR_FORCINF_TEST 作为测试类型时,测试将注入人工的1位/2位 ECC 故障。

此选项用于 CCM5F 自检。 在 CCM 错误强制模式下、不匹配的测试模式应用于 CCM-R5F (0x5应用于 CPU1、0xA 应用于 CPU2)。 错误强制完成后、ESM 错误标志"CCM-R5F - CPU 比较"和"CCM-R5F 自检错误"预计将出现。 如果这些标志未生效、则测试失败。

此时,ESM 中断可以启用或解除以响应可纠正/不可纠正的故障。 对吗?

可以。 在 SDL 示例代码中、仅针对其中一种测试模式启用 ESM 中断。

第二,如果我们使用 XXX_error_forcing_test_fault_inject,则将注入不可纠正的故障,

此模式也用于 CCM-R5F 测试。 注入到 CCM-R5F 的错误是不可纠正的。 强制执行模式错误或强制执行测试故障注入错误 需要一个周期才能完成。 之后、此模式被自动切换至锁步模式。

结构中的结果必须失败,并且 ESM 中断必须被触发,如果 ESM 中断提前启用,则必须调用回调函数。 对吗?

可以。

您好、QJ:

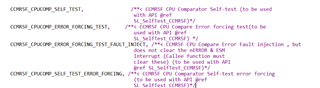

您是否是说 "CCMR5F_CPUCOMP_ERROR_CHING_TEST"用于 CCMR5F CPU 比较故障注入

是否将"CCMR5F_CPUCOMP_self_test_error_forcing"用于 CCM5F 自检故障注入?

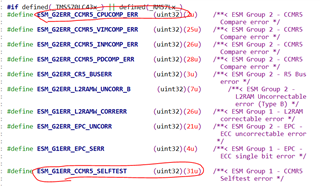

并且在错误强制完成后、ESM 错误标志"ESM_G2ERR_CCMR5_CPUCOMP_ERR"和"ESM_G1ERR_CCMR5_selftest"将相应地出现。 对吧?

如果是、"CCMR5F_CPUCOMP_ERROR_FORMATCHING_TEST_FAULT_INSD"与"CCMR5F_CPUCOMP_ERROR_FORMATCHING_TEST"相比如何?

它们是否共享相同的 ESM 错误标志"ESM_G2ERR_CCMR5_CPUCOMP_ERR"?

此外、如何选择"SRAM_ECC_ERROR_PING_1bit"?

有两个相关的 ESM 错误标志"ESM_G1ERR_L2RAMW_CORRERR"和"ESM_G2ERR_L2RAMW_Uncorr_B" 。 应该在下一张幻灯片中看到

是否完全强制出现"SRAM_ECC_ERROR_FORCE_1bit"错误?

如果可能、您可以单独介绍如何使用以下4个测试选项逐项? 何时会设置2个 ESM 错误标志呢? 这非常 令人困惑。

您好!

CPU CCM-R5F 可运行在下列四个运行模式中的一个模式下:

1.活动比较锁步模式

2.自检

3.错误强制

4.自检错误强制

"CCMR5F_CPUCOMP_ERROR_FORMATCHING_TEST" [/报价]这用于#3错误强制模式。 CCMR5F_CPUCOMP_ERROR_CHING_TEST_FAULT_INject 也用于#3错误强制模式

CCMR5F_CPUCOMP_SELF_TEST_ERROR_FORIMITH[/QUESCE]用于#4自检错误强制模式。

[/quote]并且在错误强制完成后,预计 ESM 错误标志"ESM_G2ERR_CCMR5_CPUCOMP_ERR"和"ESM_G1ERR_CCMR5_selftest"将相应地出现。 对吗?可以。

[/quote][/quote]

如果是、"CCMR5F_CPUCOMP_ERROR_FORMATCHING_TEST_FAULT_INSD"与"CCMR5F_CPUCOMP_ERROR_FORMATCHING_TEST"相比如何?

它们是否共享相同的 ESM 错误标志"ESM_G2ERR_CCMR5_CPUCOMP_ERR"?

[/报价]它们都用于#2错误强制模式。 自检错误和比较错误都已设置。

此外,如何看待"SRAM_ECC_ERROR_CHING_1bit"?

这就是 SRAM 自检。

有两个相关的 ESM 错误标志"ESM_G1ERR_L2RAMW_CORRERR"和"ESM_G2ERR_L2RAMW_Uncorr_B" 。 应该在下一张幻灯片中看到

是否完全强制出现"SRAM_ECC_ERROR_FORCE_1bit"错误?

[/报价]ESM_G2ERR_L2RAMW_Uncorr_B 已设置

您好、QJ:

我已在另一篇文章中更新了测试结果:

您好、沈明、

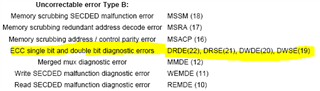

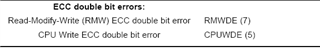

SRAM 使用单位校正双位检测(SECDED)方案由数据路径上的 ECC 进行保护。 ECC 或数据上的任何一位错误都将被自动纠正。

生成2位 ECC 错误(ESM 3.3)非常容易:

1.打开 CCS 内存浏览器、显示0x08000000 (DATA)和0x08000000 (ECC)的内容

2.将0x0000000000000000写入0x08000000、0x08000000处的 ECC 模式变为0x0C0C0C0C0C0C0C0C

3.禁用 ECC 检测和校正: sl_l2ramwREG->RAMCTRL = 0x05050005;

4.将0x0000000000000003写入 0x08000000

5.启用 ECC 检测和校正: sl_l2ramwREG->RAMCTRL = 0x0505000A;

6.从0x08000000读取数据,-->生成2位 ECC 错误(ESM 3.3)且 RAMErrStatus = 0x80

SRAM 自检将生成诊断 ECC 错误: