主题中讨论的其他器件: SysConfig

工具与软件:

1.我已经将 L2缓存设置为64K、我想知道 DSS L2和 DSS L3的共享 RAM 之间的频率差异? DSS L2 RAM 只有320K、这是不够的(在此处放置了堆栈300K)。 其他数据、以及。 文本放在 DSS L3中(猜这是原因?) 测试还发现、当放置在 L3中时(改变堆栈位置)、性能将显著降低。 我们如何对其进行优化?

2.如何改变 CPU 的时钟速度450MHz?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

1.我已经将 L2缓存设置为64K、我想知道 DSS L2和 DSS L3的共享 RAM 之间的频率差异? DSS L2 RAM 只有320K、这是不够的(在此处放置了堆栈300K)。 其他数据、以及。 文本放在 DSS L3中(猜这是原因?) 测试还发现、当放置在 L3中时(改变堆栈位置)、性能将显著降低。 我们如何对其进行优化?

2.如何改变 CPU 的时钟速度450MHz?

您好:

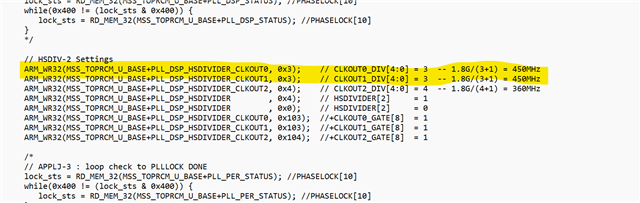

对于 AM2732 DSP、默认速度为450MHz。 我已经在 C:\ti\ccs1271\ccs\ccs_base\emulation\boards\evm_am273x\gel\evmam273x.gel 中验证了 GEL 配置文件。 DSP 时钟配置遵循 TRM 第1275页的第6.3.1章说明。 它来自内部 PLL_DSP_CLK。

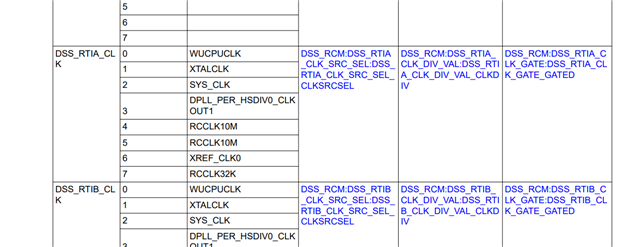

SysConfig 工具更改的时钟定义为 DSS_RTIA 时钟、您可以在 TRM 上发现它是另一个不同的外设时钟、AM27x 设置该时钟为200MHz。 因此、您不需要更改在450MHz 上运行的默认软件 DSP。

此致!

Han Tao

高 BL:

我不确定你们的方案部门有多大。 堆栈扇区大小高达30万。

建议您提供编译映射文件并检查主程序大小。 如果 C66程序都在一个主循环上、请勿使用中断功能、我们可以考虑使用乒乓 EDMA 处理程序扇区代码、因为所有函数都是逐序列处理。 可以使用手动方法将功能组合到64K 大小、并将乒乓操作复制到 L2 384K 大小。

但我们不能在 AM27x C66 DSP 内核上尝试它。 我们尝试了 Autosar OS 的 R5F 代码、可以正常工作。 短缺是每次修改程序部门需要手动方法分析映射文件并将功能组合到小64K 大小,它不容易实现。

BR!

Han Tao

e2e.ti.com/.../uart_5F00_echo_5F00_callback.Release.txt

您好、Tao、

已提供编译的映射文件。 该方法可以提高多少性能?

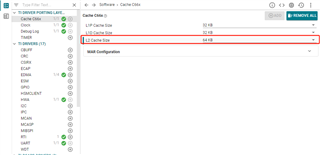

DSS L2中是否包含64K L2高速缓存?

高 BL

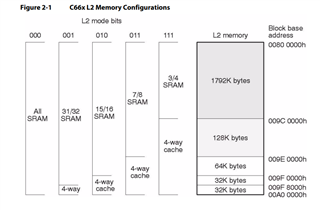

根据您的 MAP 文件、DSS_L3约为1.4MB、而 DSS_L2约为320KB。 您可以通过调整 L2高速缓存大小来试验程序的性能。 根据 AM273x TRM、在用于 L2缓存的384KB DSS_L2中、您最多可以有256KB 的内存。 当然、如果您使用 DSS_L2进行缓存、则不能将 DSS_L2用于 SRAM。 您将需要找到一个折衷点来最大化您的程序性能。 有关 C66x 高速缓存的详细信息、您可以参阅以下文档: C66x DSP 高速缓存用户指南(TI.com) 2.2配置 L2高速缓存

此致、

Ming