Other Parts Discussed in Thread: TAC5212, AM2732, SYSCONFIG

主题中讨论的其他器件: AM2732、 SysConfig

工具与软件:

我正在考虑将 TAC5212用于非音频应用和无线电应用、我将在其中使用它通过与 McASP 连接的 TI DSP 进行 I/Q 调制和解调。 此芯片是否会有适用于 FreeRTOS 的驱动程序?

二是读过类似的纯 ADC 芯片的 ADC 方面的内容、在更高的频率下会有很大的信号、甚至是3MHz 以上。 从"TLV320ADCx140、TLV320ADCx120、PCMx120-Q1、

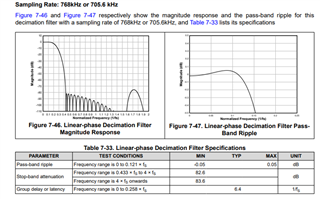

PCMx140-Q1集成模拟抗混叠滤波器和灵活数字滤波器"的项目中所示、该器件在~μ s 6MHz 处采样并使用数字滤波执行抗混叠滤波。 但我认为我需要一个滤波器来阻止高于3MHz 的频率、对吗? (实际上、我的滤波器的起始频率略高于100kHz、确保它是稳定的1MHz 高于100kHz。)

在 DAC 上、我找不到类似的文档。 我假设在器件的采样率下会有很大的采样噪声。 那么、我是否需要在输出侧使用类似的滤波器?

最后、数据表提到了3种不同的音频带宽、即90kHz (第9页、"输入信号带宽")、96kHz (ADC/DAC_CHx_BW_MODE)和100kHz (ADC/DAC 信号链部分)、 究竟是什么? 它是否真的需要宽带模式下的216kHz 采样速率、如讨论100kHz 的部分所说的那样?

谢谢!

-Corey