Other Parts Discussed in Thread: TAS5760XXEVM

尊敬的团队:

我们正在评估音频放大器,可以选择将外部 MCLK 提供给 IC,因为我 有一些疑问

1) 1)我正在播放不同类型的音频、但我只获得48MHz 的更改采样频率的方法

2) 2)如果我想为外部 MCLK 提供原理图中所需的更改。

在此阶段、请帮助我们

谢谢

Pooja AK

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TAS5760XXEVM

尊敬的团队:

我们正在评估音频放大器,可以选择将外部 MCLK 提供给 IC,因为我 有一些疑问

1) 1)我正在播放不同类型的音频、但我只获得48MHz 的更改采样频率的方法

2) 2)如果我想为外部 MCLK 提供原理图中所需的更改。

在此阶段、请帮助我们

谢谢

Pooja AK

HELO Jesse

是的,您的底衬是对的!我们 在 PurePath 控制台中使用了 TAS5760xxEVM 电路板 Rev (F),也是如此。

但我们面临时钟错误。

我必须澄清一点

这里我们给了外部 振荡器的 MCLK 、从 EVK 获取时钟的再管理、像 LRCLK、SCLK 这样的一切、我应该采用外部振荡器还是什么?

请您在这方面帮助我们

谢谢、

Pooja Ak

你(们)好

MCLK 输入由 lrclk、SCLK 分开。

如果 Fs 有一个小位移、MCLK 不会一起位移、那么每个 clk 之间的关系可能会崩溃。

您可以保持 MCLK 固定、但另一个时钟 应该具有以下关系( 在 您的情况下)。

MCLK = 256fs。SCLK = 64fs。 (如果 MCLK 不能改变、256和64必须保持稳定。也许您需要从 EVK 调整一点 FS)

但对于您的情况、即使您不更改 FS、时钟也应该能够工作。

可能其他一些根本原因会导致您的问题。

您能帮助确认每个时钟的波形和频率吗?

还要检查序列是否正常?

对于根本原因分析、您能否尝试使用具有特定值的较小 MCLK 时钟、如128xfs 或192xfs。

PS。当您尝试新时钟时、请记住清除错误并通过切换 SPK_SD 引脚恢复正常运行。

有关详细信息、您可以在数据表中查看8.3.3。

谢谢。

Jesse

此处随附示波器截图。

提前感谢您。

此致、

CSC

你(们)好

1.before 您连接了来自外部 MCU 的所有 clk 信号、是否清除了先前的 clk 错误问题产生的时钟错误?

我检查了您发送给我的时钟图、在测试期间、SCLK 似乎从3.07MHz 移动到2.82MHz、这不是稳定的、但 MCLK 非常稳定。

这是一个测试问题还是您的 SCLK 不稳定。

除了 clk 错误、您能否帮助确认是否可以从其他寄存器中找到任何其他错误?

你好,Wei

1) 1)当我连接外部 MCLK 时、仅会遇到时钟错误问题。

2) 2)我将尽快分享正确的工作条件图和非工作条件图

3)是的、有一段时间会遇到过流错误、但我们没有遇到任何问题。

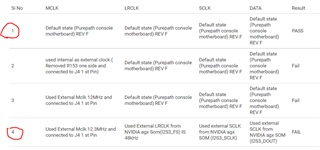

请找到我尝试不同组合的共享下表,并找到结果。

| SI 编号 | MCLK | LRCLK | SCLK | 数据 | 结果 |

| 1 | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 通过 |

| 2. | 在内部用作外部时钟(移除了一侧的 R153并连接到 J4 1 st 引脚) | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 失败 |

| 3. | 已使用外部 MCLK 12MHz 并连接至 J4 1 st 引脚 | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 默认状态(PurePath 控制台主板) REV F | 失败 |

| 4. | 已使用外部 MCLK 12.3MHz 并被连接至 J4 1 st 引脚 | 已使用 NVIDIA agx Som (I2C3_FS)的外部 LRCLK 为48kHz | 已使用 NVIDIA agx SOM 的外部 SCLK (I2C3_SCLK) | 已使用 NVIDIA agx SOM 的外部 SCLK (I2C3_DOUT) | 失败 |

谢谢、

Pooja Ak

尊敬的 Jesse J

上述问题的现状。

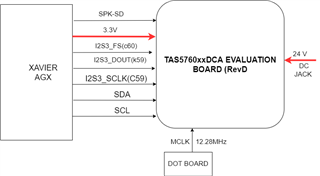

我们用 Xavier AGX 板替换了 PPCB、并连接 到 TAS5760xxEVM、修订版 D

请查看以下电路板更改、如果需要对硬件进行任何更改、请建议我们执行此操作。

1) 1)从 Xavier AGX 中连接了所有 LRCLK、SCLK 和 DIN。

2) 2)连接的 MCLK 12.28MHz。

3) GAIN0和 GAIN1被设为高电平(3.3V)

4) 4) SPK SD 引脚提供了2个可选的低电平和高电平

请您帮助我们解决这一问题,我们从过去20天开始就一直在努力解决同样的问题。

谢谢、

Pooja Ak

你(们)好

让我澄清一下这个问题。

1.我看到您有时遇到过流错误、 您是否找到了根本原因? 发生频率如何?

2.在4种情况下、您能否按照与1中的时钟相同的方式调整4中的时钟、然后对它们进行比较以查看是否有差异?

3.上次给我发送时钟 wav 时,我发现 SCLK 时钟不稳定,测试 期间从3.07->2.82MHz 变化,是测量误差还是时钟不稳定。

4.您能给我一张简单的图表,说明您如何连接每个时钟,以便更好地理解。

尊敬的 Jessi Ji:

e2e.ti.com/.../non-working-clk-images.zip1)在初始阶段、我们遇到 过流错误、然后自动其关闭。

2)我们的目标是使用 NVIDIA 进行验证,这样我们就不能检查当前的问题了,而是从 ppcmb 替换为 NVIDIA。

到目前 为止、我们已将 PPCB 替换为 Xavier AGX 板、并连接到 TAS5760xxEVM、修订版 D

请找到所附的方框图,以便于您的折射,您可以通过该方框图进行讨论,从而轻松地发现问题

请对此提供支持

谢谢、

Pooja AK

AK

您能给我发送每个时钟信号的波形吗?

当 MCLK 与其他时钟相分离时、更容易发生时钟误差。

因为时钟抖动可能与每个时钟源不同、所以它们的同步关系被打破。

这是我的电子邮件。 jesse-ji@ti.com。

我们可以通过电子邮件进行交谈。

谢谢。

Jesse

尊敬的 Jesse

我刚刚浏览了音频论坛,您的一位客户遇到了与我们相同的问题( https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1091769/tas5760m-inquiry/4043588?tisearch=e2e-sitesearch&keymatch=%25252525252520user%2525252525253A357730#4043588 )

我在这里为您的折射附上了折射链接,请告诉我它们是如何在最后生成 MCLK 的,所以它也将被我使用。以发现 时钟 误差问题

在我们的末尾、64位和单声道模式中、除了 它们都是相同的。

请求您帮助。

谢谢、

Pooja Ak