https://e2e.ti.com/support/audio-group/audio/f/audio-forum/903168/tlv320adc3100-bclk-settings

器件型号:TLV320ADC3100大家好、

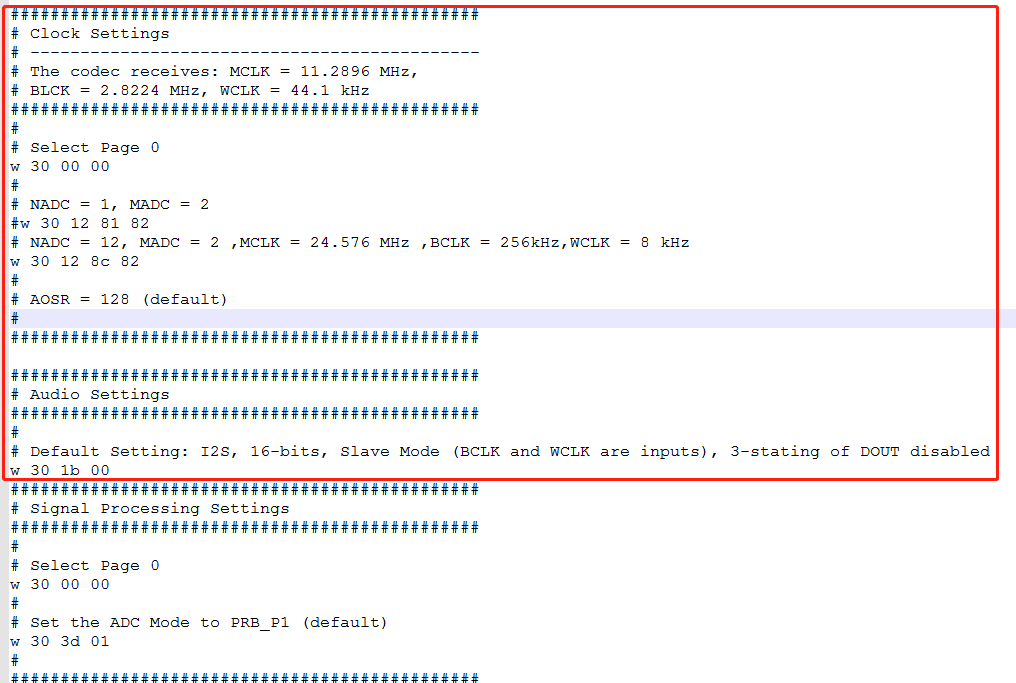

我正在尝试了解如何设置 TLV320ADC3100的 BCLK、我的理解是在从模式下、主机应向 ADC 提供 BCLK、该 BCLK 应为2 *采样频率*字长(多少位)。

当 I2S 字长为16位且采样频率为44.1kHz 时、BCLK 应为1.4112MHz、而在数据表的示例中、BCLK 为2.8224MHz (16位字长)、如何理解?

谢谢

乔治