您好!

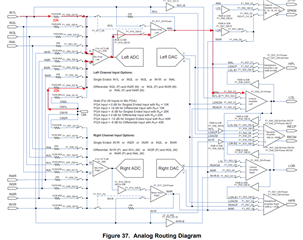

我们在我们的设计中使用了 TI 编解码器部件 TLV320AIC3268IRGCT。 在编解码器验证过程中、我们已经看到 ADC 输出数量少于实际输入正弦信号振幅。

我们在编解码器输入前使用一个 VOGAD IC、这样、在编解码器 ADC 输入上大约1Vpp 至1.2Vpp 的电压将一直可用。 ADC 输入满量程范围应支持0.5Vrms 或1.414Vpp。

如果我们提供1Vpp 的输入振幅、ADC 输出的振幅仅约为+-500个计数、这明显小于输入振幅。 我们在 ADC 前端获得+-500次计数和0dB PGA 增益 如果我们将 PGA 增益增加到+6dB、计数就会增加。 如果 PGA 增益增加至+12dB、ADC 计数将达到大约+-2500并达到饱和。 但 ADC 应在约为+-32000的满量程范围计数处饱和。

下面是用于查看的编解码器寄存器配置。

注意:编解码器 DAC 使用 FPGA DDS 通过输出正弦信号进行独立验证。 我们面临 ADC 性能问题。

此致

Hafiz Haja.