主题中讨论的其他器件: DRV134、 DRV135

我们以前 一直使用 TLV320ADC3101来监测差分信号。 我们现在需要器件来监测单端信号。

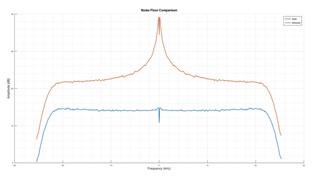

我们在输入设置为差分和单端的情况下测量了噪声水平(即输入引脚悬空)。

我们相信我们已正确设置"音频输入路径"、可在端口上注入信号。

在比较噪声级别与频率之间的关系时、我们可以看到以下情况:

从数据表中寄存器52的脚注中我们预计单端的噪声水平要高6dB。 (是这样吗?)

然而、在单端情况下、在较低频率看到的"肩"对于我们的应用来说是一个非常严重的问题。

Question:

1.在单端操作中、噪声水平是否预计会在频带下端快速升高?

2.您是否可以建议采取任何缓解措施来降低频谱下端的噪声?

3.我们是否必须使用不同的 ADC 才能获得更好的单端性能?建议是什么?