https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1313360/pcm5102a-dac-output

器件型号:PCM5102A您好!

我们将在4线 I2S 模式下针对非音频频率使用 PCM5102A。 所有时钟(SCK、LRCK、BCK)和 DIN 均从 FPGA 生成并馈送到 DAC。

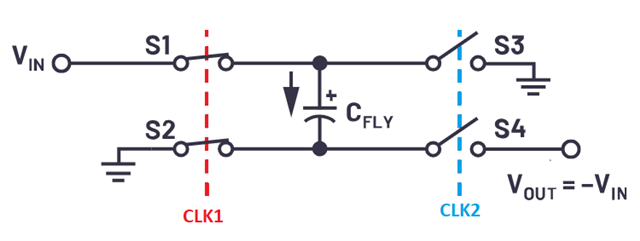

我们也尝试将此电路用于常见的音频频率。 但对于32KHz 的频率、DAC 输出也不会出现。 随附了原理图、供您参考。 请查看并告诉我您的评论。 我列出了我们测试电路时的以下观察结果。 VNEG 电压为0V、这是什么原因? 这会影响 DAC 输出吗?

1. LDO 电压为1.92V

2. VNEG 电压观察为0V。

3. CAPP 和 CAPM 上无法观察到电压。

4. I2S 图符合图14数据表中的预期。 已连接快照。

此致、

水烟五世