大家好!

在我们调整在 LINE1LP 引脚中接收的麦克风信号的电平(在单端模式下)并通过 LEFT_LOP 输出的情况下、我们使用 TLV320AIC3106。

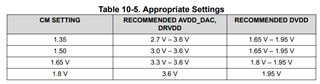

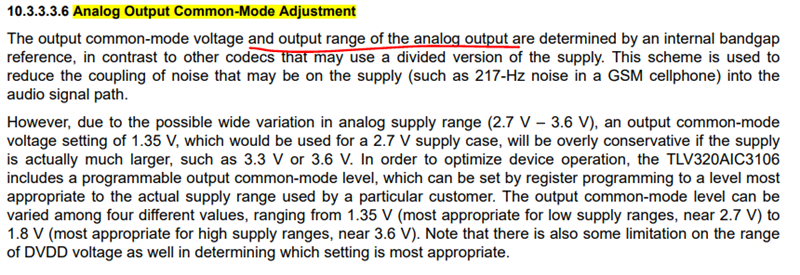

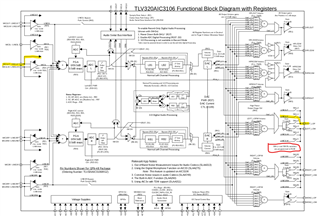

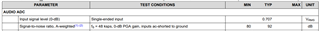

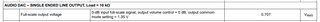

我们最近意识到 LEFT_LOP 输出的信号饱和略低于2.7V Vpk-pk。 在查看数据表后,我们检测到以前没有注意到的设置:" 模拟输出共模调整"。 浏览数据表后 、我们最终发现" 页0/寄存器40:高功率输出级控制寄存器 "之后、我们将位 D7-D6从00修改为10、因为我们 IC 使用3V3为 IOVDD/DRVDD 供电、并使用1V8为 DVDD 供电。

我们再次检查了 LEFT_LOP 输出电压饱和电平... 遗憾的是、没有变化、输出仍在略低于2.7V Vpk-pk 时达到饱和、因此我们似乎缺少一些东西。

现在、我们有以下问题:

- 输出共模调节 是否按预期工作? 我的意思是:

- 它会影响单端和差分模式下的 LEFT_LOP 输出行为

- 如果 D7-D6 = 00、则 LEFT_LOP 输出 信号将在2V7饱和。

- 如果 D7-D6 = 10、则 LEFT_LOP 输出 信号将在3V3处饱和。

- " 页0/寄存器40:高功率输出级控制寄存器 是不仅修改 HPLOUT 而且修改 LEFT_LOP 输出输出输出共模调整的右侧寄存器。 我提出这个问题,是因为登记册的名称有些误导。

- "页0/寄存器42:输出驱动器弹出抑制寄存器"位 D1可以与此主题相关吗?

- 如果在我们的电流配置 (D7-D6 = 00)下、输出信号会在2.4V 以上而不是2.7V (Vpk-pk)达到饱和。 这是否意味着我们 限制输出电压的方式与使用 模拟输出共模调节时不同? 如果答案是肯定的,则:

- 如果我们无意中将该输出电压范围限制为2.4V、 D7-D6位值是否会产生影响? 或者由于信号限制在较早的2V4、将其配置为2V7或3V3无关紧要?

- 什么寄存器也可能影响输出电压范围?

对于我们可能会犯什么错误、您有什么指导吗? 请勿使输入信号约为2.3V (Vpk-pk)并且未达到饱和。

提前感谢您的参与!

此致、