请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:F29H859TU-Q1 工具/软件:

尊敬的专家:

我对 IO 引脚的行为有疑问。

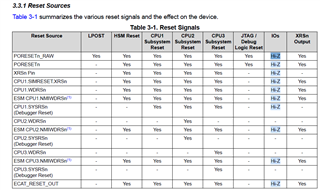

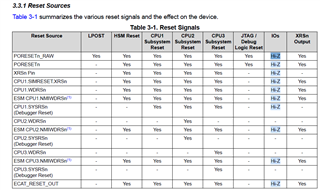

众所周知、复位后、IO 引脚进入高阻抗(HI-Z)状态。 您能否说明在哪些其他条件下 IO 引脚也可能进入高阻抗状态?

PWM 跳闸区是否会导致 IO 高阻态?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

我对 IO 引脚的行为有疑问。

众所周知、复位后、IO 引脚进入高阻抗(HI-Z)状态。 您能否说明在哪些其他条件下 IO 引脚也可能进入高阻抗状态?

PWM 跳闸区是否会导致 IO 高阻态?

尊敬的 Lawrence:

请参阅以下主题。

[引述 userid="623730" url="~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1514173/f29h859tu-q1-inquiry-conditions-for-io-pins-entering-high-z-statePWM 跳闸区是否会导致 IO 高阻态?

[/报价]例如、可以在 NMI 处理程序中触发 PWM、以通过软件写入 TZFRC 寄存器来强制关闭 PWM。 或者、您可以在发出任何将导致 GPIO 进入默认状态或高阻抗的系统复位之前使用硬件事件将输出触发为低电平。

此致、

Ryan Ma