工具/软件:

尊敬的专家:

美好的一天! 我要找客户。

我的客户面临中断问题:现在每100ms 触发一次 PWM 中断、但 PWM 中断中的代码将至少运行120ms。 这意味着当 CPU 进入 PWM 中断时、当下一个中断触发 到来时、CPU 仍将在中断函数中运行。

客户想知道在 ePWM 中断功能中、是否有办法确定 MCU 中是否有另一个中断挂起?

谢谢!

此致

Kita

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

美好的一天! 我要找客户。

我的客户面临中断问题:现在每100ms 触发一次 PWM 中断、但 PWM 中断中的代码将至少运行120ms。 这意味着当 CPU 进入 PWM 中断时、当下一个中断触发 到来时、CPU 仍将在中断函数中运行。

客户想知道在 ePWM 中断功能中、是否有办法确定 MCU 中是否有另一个中断挂起?

谢谢!

此致

Kita

尊敬的 Delaney:

这是一个紧急情况,可能需要您的帮助检查今天,谢谢!

我的客户现在面临以下问题:

这是他的代码:

客户发现、在中断函数中、有时他使用 ETCLR 来清除中断、但 CPU 仍可输入 if (EPWM4Regs.ETFLG.bit.INT)。 这意味着 ETCLR 无法清除 ETFLG 或在清除 ETFLG 后再次设置。 在这种情况下、ISR 执行时间可能长于 ISR 触发时间。

我不确定为什么 ISR 执行时间超过 ISR 触发时间会导致 CPU 仍可以进入 if (EPWM4Regs.ETFLG.bit.INT)。 您能给我一些建议吗?

谢谢!

此致

Kita

尊敬的 Kita:

我对你的问题有点困惑。 使用 ETCLR 寄存器清除 ETFLG 将允许进一步的中断输入。 这是所需的行为、对吧? 如果在设置 ETFLG 位之后出现另一个中断、则该中断将处于挂起状态、直到当前 ISR 执行完毕。 之后、PIE 将评估哪个中断是已标记(挂起)和已启用的中断的最高优先级。 如果这与之前相同的中断、它将再次执行该 ISR。 对于此应用、如果您不希望错过任何进一步的触发条件、我建议在 ISR 开始时清除 ETFLG 位。

另外、这两个 NOP 在其代码中的作用是什么? 这也会增加 ISR 时间。

此致、

Delaney

尊敬的 Kita:

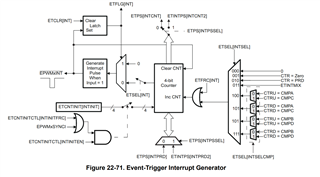

这是 TRM 中的图、您可以在 ePWM 一章的事件触发器一节中参考:

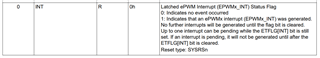

以下是 ETFLG[INT]寄存器说明:

请注意、它规定当该位设置为1时、"表示生成了 EPWMx 中断(EPWMx_INT)。 在清除标志位之前、不会再生成中断。 在 ETFLG[INT]位仍设置时、最多可以挂起一个中断。 如果有一个中断挂起、在清除 ETFLG[INT]位之前不会生成该中断 "

如该说明中所述、可能有一个中断挂起。 如果有一个中断挂起、它将在使用 ETCLR[INT]位清除标志后立即执行。 正如说明中所述、然后会设置中断标志、以指示生成了另一个 EPWM 中断。

此致、

Allison