请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F28P650DK 主题:SysConfig 中讨论的其他器件

工具/软件:

您好、工程师:

我测试了使用库函数进行操作的方法、这会占用大量 CPU 时间。 与直接寄存器操作相比、差异为10倍。 在以下程序中、 endat22_reset_CLB() 函数是例程提供的库函数、而 RstCLB_endat22() 函数是 ME 修改的寄存器配置函数。 我进行了一些修改、逐一进行了比较。

使用 endat22_reset_clb()时、可以按预期发送和接收数据;但是、用 RstCLB_endat22()替换数据无法正常发送数据。

替换后、CLB 寄存器中的更改相同、但 CLB 无法按预期运行。

void endat22_reset_CLB(void)

{

CLB_setGPREG(CLB4_BASE, 0);

//

// Turn OFF the CLB functionality

//

EALLOW;

HWREG(CLB4_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

//

// Clear and reload the HLC registers

//

CLB_writeInterface(CLB4_BASE, CLB_ADDR_HLC_R0, 0x9);

CLB_writeInterface(CLB4_BASE, CLB_ADDR_HLC_R1, 0x0);

CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_1_MATCH1, 0x2);

CLB_setOutputMask(CLB4_BASE, 0, false);

//CLB3

CLB_setGPREG(CLB3_BASE, 0);

//

// Turn OFF the CLB functionality

//

EALLOW;

HWREG(CLB3_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

//CLB2

CLB_setGPREG(CLB2_BASE, 0);

//

// Turn OFF the CLB functionality

//

EALLOW;

HWREG(CLB2_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

//CLB1

CLB_setGPREG(CLB1_BASE, 0);

//

// Turn OFF the CLB functionality

//

EALLOW;

HWREG(CLB1_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

CLB_writeInterface(CLB1_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

}

void RstCLB_endat22(void)

{

// CLB_setGPREG(CLB4_BASE, 0);

Clb4LogicCtrlRegs.CLB_GP_REG.all = 0;

//

// Turn OFF the CLB functionality

//

EALLOW;

// HWREG(CLB4_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

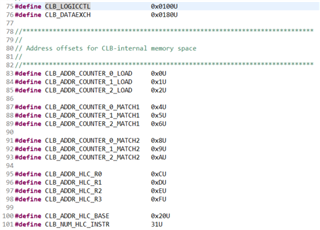

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 0;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 1;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 2;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

//

// Clear and reload the HLC registers

//

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_HLC_R0, 0x9);

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_HLC_R1, 0x0);

// CLB_writeInterface(CLB4_BASE, CLB_ADDR_COUNTER_1_MATCH1, 0x2);

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 0xC;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0x9;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 0xD;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb4LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x5;

Clb4LogicCtrlRegs.CLB_LOAD_DATA = 0x2;

Clb4LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

// CLB_setOutputMask(CLB4_BASE, 0, false);

Clb4LogicCtrlRegs.CLB_OUT_EN &= ~((Uint32)0);

//CLB3

// CLB_setGPREG(CLB3_BASE, 0);

Clb3LogicCtrlRegs.CLB_GP_REG.all = 0;

//

// Turn OFF the CLB functionality

//

EALLOW;

// HWREG(CLB3_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

Clb3LogicCtrlRegs.CLB_LOAD_EN.all = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

// CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

// CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

// CLB_writeInterface(CLB3_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

Clb3LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x0;

Clb3LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb3LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb3LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x1;

Clb3LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb3LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb3LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x2;

Clb3LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb3LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

//CLB2

// CLB_setGPREG(CLB2_BASE, 0);

Clb2LogicCtrlRegs.CLB_GP_REG.all = 0;

//

// Turn OFF the CLB functionality

//

EALLOW;

// HWREG(CLB2_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

Clb2LogicCtrlRegs.CLB_LOAD_EN.all = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

// CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

// CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_1_LOAD, 0x0);

// CLB_writeInterface(CLB2_BASE, CLB_ADDR_COUNTER_2_LOAD, 0x0);

Clb2LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x0;

Clb2LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb2LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb2LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x1;

Clb2LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb2LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

Clb2LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x2;

Clb2LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb2LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

//CLB1

// CLB_setGPREG(CLB1_BASE, 0);

Clb1LogicCtrlRegs.CLB_GP_REG.all = 0;

//

// Turn OFF the CLB functionality

//

EALLOW;

// HWREG(CLB1_BASE + CLB_LOGICCTL + CLB_O_LOAD_EN) = 0;

Clb1LogicCtrlRegs.CLB_LOAD_EN.all = 0;

EDIS;

//

// Clear Counters - this will clear counter REGs. Add_shift_on_even_en should be Zero for this to take effect.

//

// CLB_writeInterface(CLB1_BASE, CLB_ADDR_COUNTER_0_LOAD, 0x0);

Clb1LogicCtrlRegs.CLB_LOAD_ADDR.all = 0x0;

Clb1LogicCtrlRegs.CLB_LOAD_DATA = 0;

Clb1LogicCtrlRegs.CLB_LOAD_EN.all |= 1;

}

此致、

林浩南