Other Parts Discussed in Thread: TMS320F28388D

- 器件型号:TMS320F28388D

工具/软件:

尊敬的团队:

在我的当前实现中、我为每个内核配置了相同的两个中断源:

- CPU1 :ADC ISR1、eCAP1

- CPU2 :ADC ISR1、eCAP1

两个内核都由各自的 ISR 触发、但在每个内核上执行的代码不同。 ePWM 模块启动 ADC 转换启动(SOC)、在 ADC 转换完成后、ADCINT1会在两个内核上触发中断。 PWM 计时器周期约为39 µs。

此外、每个线路周期产生一次 eCAP 中断、并且还会触发两个内核。 我使用在每个 ISR 的入口点和出口点切换的 GPIO 捕获了中断波形、并在下面分享了结果。

出于测试目的、我在 eCAP1 ISR 中添加了超出 PWM 中断周期的额外计算。

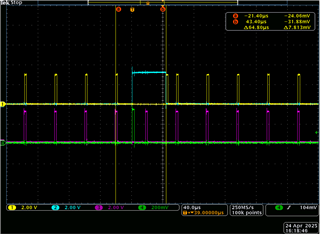

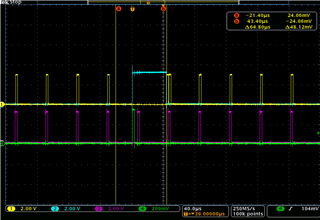

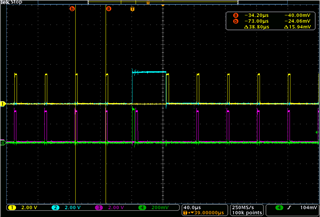

波形通道映射:

- CH1:CPU1 ADC ISR

- CH2:CPU1 eCAP ISR

- CH3:CPU2 ADC ISR

- CH4:CPU2 eCAP ISR

通常、ADC ISR 在每个39 µs 期间触发。 但是、如果在 ADC ISR 之前对 eCAP ISR 进行服务、则会延迟 ADC ISR 执行、直到 eCAP ISR 完成。

在一种情况下、eCAP ISR 在下一个 ADC ISR 之前完成、只剩下一个小窗口用于在 CPU1上执行 ADC ISR。

在另一种情况下、eCAP ISR 没有留出足够的时间、从而导致跳过一个 ADC ISR。 我的问题是:在这种情况下、CPU2为什么也跳过了 ADC ISR?

我怀疑 ADC 外设归 CPU1所有、因此它负责清除中断标志。 如果 CPU1没有清除标志、则 ADC ISR 不会再次触发。 但是、一旦 CPU1执行下一个 ADC ISR 并清除标志、CPU2也应该能够响应 ADC 中断。

我的疑问是:

- 在这些情况下、哪些情况可能会导致 CPU1和 CPU2同时缺少 ADC ISR?

- 考虑到非拥有内核无法清除中断标志、一个内核所拥有的外设(如 ePWM 或 ADC)是否可以在另一个内核上触发 ISR、而不在其自身内核上触发该 ISR?

- 鉴于 eCAP ISR 具有最低的优先级、是否有一种

EINTDINT like below在 eCAP ISR 内使用简单嵌套(使用和启用/禁用中断)来确保始终执行 ADC ISR 的有效方法?

__interrupt void ecap3ISR(void)

{

if (ECap3Regs.ECFLG.bit.CEVT1 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT1 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT2 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT2 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT3 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT3 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT4 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT4 = 0x1;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

ECap3Regs.ECCLR.bit.INT = 0x1;

EINT;

/* some code

*/

DINT;

}

4. 关于中断嵌套的最后一个问题:如果我希望 ePWM 中断抢占 eCAP ISR (来自不同的中断组)、启用该功能的步骤是什么? TI 的文档介绍了同一组内的嵌套、但不涵盖跨组的嵌套。

允许通过 ePWM 嵌套 eCAP 是否存在风险? 我想避免出现类似的情况eCAP1 -> EINT -> eCAP2 -> EINT -> ePWM、其中两个 eCAP ISR 会延迟较高优先级的 ePWM ISR。 我的目标是尽可能地减少延迟、并确保 ePWM 不会因背对背 eCAP 而延迟。