主题:C2000WARE 中讨论的其他器件

工具/软件:

尊敬的工程师:

我要使用的例程是 Ware_Motor Control_SDK_5_03_00_00\solutions\boostxl_posmgr\f28p65x。

此示例的 CLB 部分可以进行优化。 例如、结构定义太多、但不会影响功能。 我当前正在使用 BiSSc CLB 例程、发现一个问题:CLB 提供 SPICLK、但 SPIRXFIFO 忽略前 8 位、无法接收。

如果 SPI 在 SPICLK 的上升沿接收数据、则 I 接收的编码器返回数据应为 0x8777、0xBBB7、0x3BBF、0x3466。

然而、SPIFIFO[0]= 0x77BB、SPIFO[1]= 0xB73B、SPIFO[2]= 0xBF34、SPIFIFO[3]= 0x6600。

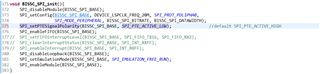

SPI 数据为 14 位、并根据例程执行配置:

在程序中、我不使用中断、而是在接下来的 62.5us 周期内接收数据。 SPIPTE 由外部 GPIO 输入并保持低电平。TxEN 保持低电平。

为什么数据接收短缺?此外、我想问为什么该例程将 SPI 数据宽度配置为 14 位、但接收掩码设置为低 12 位。

此致、

林浩南