工具/软件:

您好、工程师:

此致、

林浩南

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、工程师:

此致、

林浩南

您好 Lori、

程序的哪个部分会将 TxEn 信号保持为低电平? 这可能是造成这种情况的原因。

此外、在初始化 Endat 和 Tformat 时、我将 TxEn GPIO 重新配置为 clboutputxbar。 这是否会受到将 TxEn 信号配置为保持低电平的 BiSS-C 程序的影响?

我记得在切换通信(从 BiSS-C 切换到 Tformat 和 Endat)时、命令发送是正常的、编码器返回数据、但 SPI 不会正常接收数据。 spiRxFIFO 只有一段全为零的数据。 spiRxFIFO 中的这个数据应该是发送命令时 SPI 接收到的数据。我对此有点不确定。

我检查了开关后 tformat 和 endat 的 CLB 输出、包括 TxEn 引脚信号和生成的 SPICLK、所有这些都是正常的。 无法正常通信的原因是 SPIRX 未按预期工作。SPIRXFIFO 中的数据数量正确、但 RXFIFO 中的数据不正确。

① μ s

② μ s

③ μ s

④ μ s

⑤ μ s

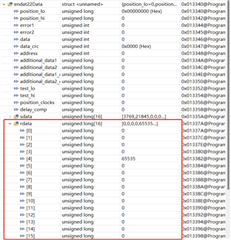

最终接收到的数据为:

我在程序中检查了 SPI 的配置、发现没有任何区别:

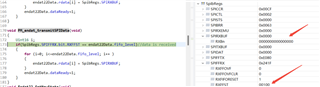

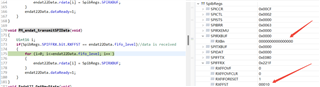

void BISSC_SPI_init(){

SPI_disableModule(BISSC_SPI_BASE);

SPI_setConfig(BISSC_SPI_BASE, DEVICE_LSPCLK_FREQ_20M, SPI_PROT_POL1PHA0,

SPI_MODE_PERIPHERAL, BISSC_SPI_BITRATE, BISSC_SPI_DATAWIDTH);

SPI_enableTalk(BISSC_SPI_BASE);

SPI_enableFIFO(BISSC_SPI_BASE);

SPI_disableLoopback(BISSC_SPI_BASE);

SPI_setEmulationMode(BISSC_SPI_BASE, SPI_EMULATION_FREE_RUN);

SPI_enableModule(BISSC_SPI_BASE);

}

void PM_tformat_Spi_Init(void)

{

SPI_disableModule(PM_TFORMAT_SPI);

SPI_setConfig(PM_TFORMAT_SPI, DEVICE_LSPCLK_FREQ_20M, SPI_PROT_POL0PHA0,

SPI_MODE_PERIPHERAL, 2500000, 10);

SPI_enableTalk(PM_TFORMAT_SPI);

SPI_enableFIFO(PM_TFORMAT_SPI);

SPI_reset(PM_TFORMAT_SPI);

SPI_disableLoopback(PM_TFORMAT_SPI);

SPI_setEmulationMode(PM_TFORMAT_SPI, SPI_EMULATION_FREE_RUN);

SPI_enableModule(PM_TFORMAT_SPI);

}

void endat22_spi_fifo_init() {

//

// Initialize SPI FIFO registers

//

SPI_disableModule(PM_ENDAT22_SPI);

SPI_setConfig(PM_ENDAT22_SPI, DEVICE_LSPCLK_FREQ_20M, SPI_PROT_POL1PHA0,

SPI_MODE_PERIPHERAL, 200000, 9);

SPI_enableTalk(PM_ENDAT22_SPI);

SPI_enableFIFO(PM_ENDAT22_SPI);

SPI_reset(PM_ENDAT22_SPI);

SPI_disableLoopback(PM_ENDAT22_SPI);

SPI_setEmulationMode(PM_ENDAT22_SPI, SPI_EMULATION_FREE_RUN);

SPI_enableModule(PM_ENDAT22_SPI);

}