工具/软件:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我不太明白这里的问题。

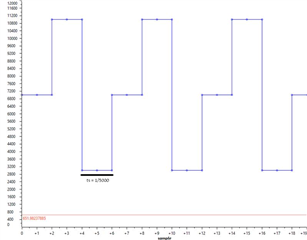

为了应对这个问题、我设置了一个变量、使其“错过“载波的前半个周期(在第一个 ISR 触发器中传递代码的一个简单的 IF 条件)、这样就可以“移动“代码 180 度。 如下图所示:

您如何通过丢失前半个周期来换档 180 度?

我还尝试将 TBCTR 设置为与 TBPRD 相同的值、以强制载波从顶部开始、如 PLECS 中所示、但这也不起作用。 [/报价]你能用简单的图表解释你试图实现什么和你在相同的波形得到什么? 你说不起作用的时候,我不明白这里的问题是什么。 我所看到的是互补 PWM 信号

谢谢

你好 Prarthan、

当然、让我用更简单的术语解释一下我的问题。

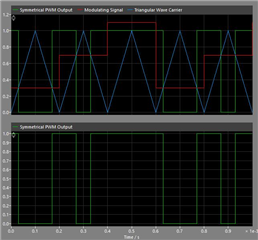

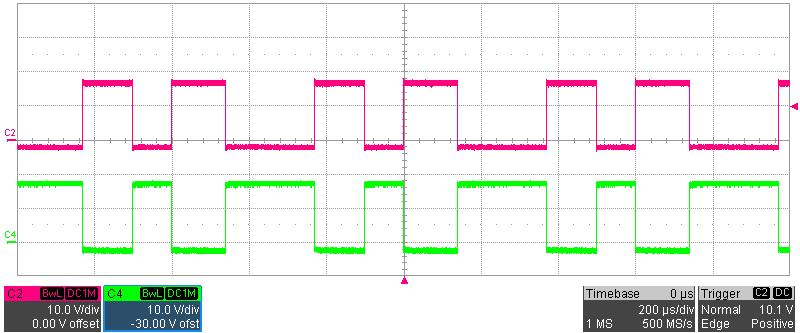

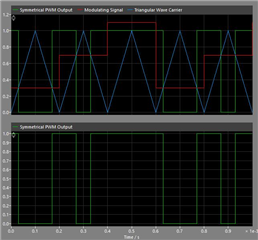

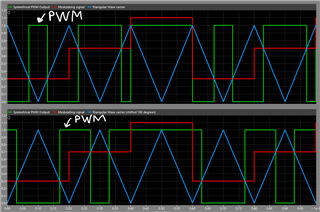

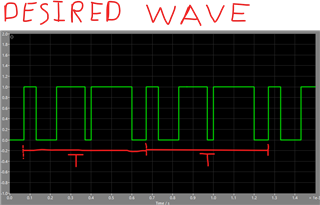

下图显示了 PLECS 内的两种不同示波器捕获。

绿色:PWM 输出。

红色: 调制信号、这在两次捕获中是相同的。

蓝色: 三角载波、 在 顶部的捕获中从 1 开始、而在 底部的捕获中从 0 开始。 这意味着 顶部和底部载波相距 180 度。

我要实现 PWM 输出波形 ( 绿色 )、如所示 顶部 捕获、但在尝试许多不同的操作后、我在示波器中只看到所示的 PWM 输出 底部 采集(如所示) 深粉红色 在原始 POST 的实际示波器上)。

您如何通过丢失前半个周期来移动 180 度?

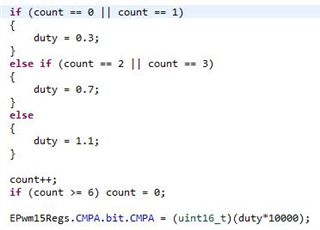

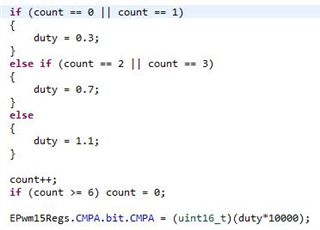

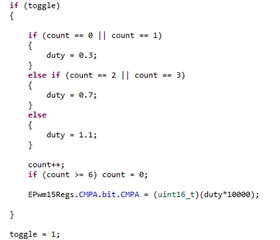

当我意识到 PWM 输出不是我想要实现的波形时,我尝试使用变量“丢失“第一个中断例程“ 切换 “、试图让代码在下一个中断周期开始。 载波是一个三角波形、会触发 顶部和底部的 ADC 中断。

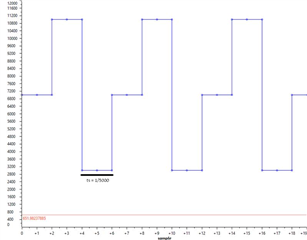

此变量初始化为 0。 在第一个中断中、它绕过 所需的代码。 下面的图片很清晰、并解释了我的意思。

如果 我可以提供更多信息、请告诉我。

再次感谢 !

您好、

[引用 userid=“661156" url="“ url="~“~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1536086/tms320f28p650dk-pwm-cmpa-update-problem/5911675 #5911675“]

绿色:PWM 输出。

红色: 调制信号、这在两次捕获中是相同的。

蓝色: 三角载波、 在 顶部的捕获中从 1 开始、而在 底部的捕获中从 0 开始。 这意味着 顶部和底部载波相距 180 度。

是的、上述值应该可以通过启动 TBPRD 中第二个 PWM 的计数器来实现。 对于 TBCTR 初始值、可以将其设置为 TBPRD。

确保禁用 TBCLKSYNC 和 GTBCLKSYNC、然后执行 PWM 初始化、然后在 EPWM 初始化完成后启用 TBCLKSYNC。

此外、确保比较值的影子加载在所需的时间 bas 事件发生。 从上面的信号看起来像顶部 PWM 波形、比较值在 COUNTER = TBPRD 时变化、而底部 PWM 波形则比较值在 Counter=ZERO 时变化。 在事件发生之前、计数器值也应更新为影子寄存器。

谢谢

你好 Prarthan、

CMPA 更新在载波的每个顶部和底部进行。 尽管从图片上看起来并不像、但实际上是 通过为两个连续中断保持相同的值来实现的、这就是为什么只在顶部或底部看到更新的原因。

我在 PWM 初始化之前尝试禁用 TBCLKSYNC 和 GTBCLKSYNC、稍后再启用这两种模式、但没有用。

我还尝试将计数器设置为从 TBPRD 开始或从 0 开始、但我想要实现的波形(最上面的示波器捕获)仍然没有显示。

影子寄存器被设置为顶部和底部 (CMPCTL.bit.LOADMODE = CC_CTR_ZERO_PRD)。 我甚至尝试更改这些值,以更新在顶部只有稍后在底部只有,也没有任何作用。

我真的很困惑、因为我似乎无法让第一个波形出现、尽管它是一个非常简单的调制。

在事件发生之前、计数器值也应更新为影子寄存器。

在这种情况下、该计数器到底会是什么? 如前面所示、CMPA 寄存器已在零和 TBPRD 处更新。 但我不确定现在会是什么。

感谢您的支持!

您好、

您能否在示波器波形中显示缺少的内容? 我无法将示波器屏幕截图与 PLECS 示波器输出相关联。

您要显示的示波器屏幕截图、顶部和底部 PWM 波形是什么? 它们的输出是否是相同的 EPWM 含义 epwma 和 epwmb? 或者它们是不同的 PWM 实例输出吗?

如果您希望相同的通道 PWM 输出、pwma 和 pwmb 在时间上重叠,那么为什么您的 ePWM 处于互补模式?

载波的每个顶部和底部都进行了 CMPA 更新。

我不明白为什么要在 PRD(顶部)和零(底部)更新比较值、因为如前所述、比较值仅在这两个事件中的任何一个发生时才会影子加载到活动状态。

在这种情况下、此计数器到底会是什么? 如前面所示、CMPA 寄存器已在零和 TBPRD 处更新。 但我不确定现在会是什么。

影子到活动加载事件决定了影子寄存器中的值何时加载到活动寄存器中(有效的值)。 如果未更新、则影子加载影子寄存器中的先前值或现有值。

谢谢

你好 Prarthan、

您能否在示波器波形中显示缺少的内容? 我无法将示波器屏幕截图与 PLECS 示波器输出相关联。

您要显示的示波器屏幕截图、顶部和底部 PWM 波形是什么? 它们的输出是否是相同的 EPWM 含义 epwma 和 epwmb? 或者它们是不同的 PWM 实例输出吗?

如果您希望相同的通道 PWM 输出、pwma 和 pwmb 在时间上重叠,那么为什么您的 ePWM 处于互补模式?

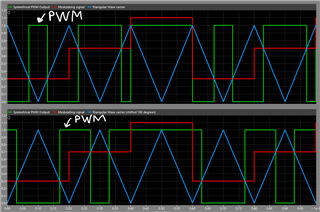

[/报价]我将以不同的方式进行解释。 我来说明一下我的意思。

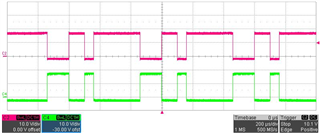

左图:我想要的一个,就像在 PLECS 中一样。

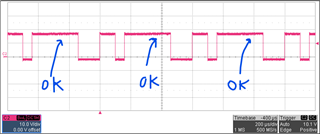

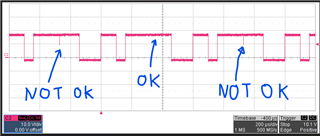

右图:从实际示波器中获得的图像。

用于生成它们的代码完全相同。 并在载波波形的顶部和底部进行更新。

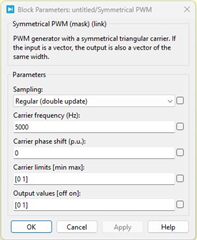

我不明白为什么要在 PRD(顶部)和零(底部)更新比较值、因为正如我前面提到的、比较值仅在这两个事件中的任何一个上影子加载处于活动状态。 [/报价]是的、在这种情况下您是对的、它可以只在顶部更新或只在底部更新、但这不应该是问题、因为 CMPA 值 在两个中断周期内被编程为相同。 从 PLECS 中可以看到、我使用的 C 脚本与 Code Composer Studio 中的 ADC_ISR 完全相同、两者都在顶部或底部触发。 如果需要、我也可以共享完整的 PLECS 文件。

[引用 userid=“559325" url="“ url="~“~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1536086/tms320f28p650dk-pwm-cmpa-update-problem/5914314 #5914314“]影子到活动加载事件决定影子寄存器中的值何时加载到活动寄存器(有效的值)。 如果未更新、则影子加载影子寄存器中的先前值或现有值。

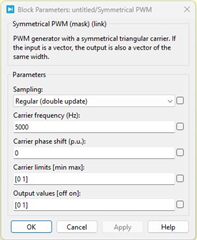

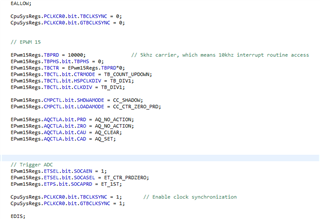

我知道、但这不是已经通过 PWM INIT 编程的内容、如下所示?

然后、我尝试将 TBCTR 寄存器处的计数器开始位置(从 0 或 TBPRD 开始)更改为无可用。 波形看起来不像我预期的那样。 然后我将 SOCASEL 更改为仅在底部更新、稍后仅在顶部更新、但没有一个会提供 PLECS 中所示的期望波形。

如果还有其他我可以分享的内容、请告诉我。

感谢您的帮助!

您好、

[报价 userid=“661156" url="“ url="~“~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1536086/tms320f28p650dk-pwm-cmpa-update-problem/5914449 #5914449“]左图:我想要的一个,就像在 PLECS 中一样。

右图:从实际示波器中获得的图像。

获得的波形的区域。 什么不匹配?

所需波形中第二个脉冲后的间隙缺失? 其他脉冲/波形是否匹配?

这意味着顶部 PWM 中 缺少下降事件(CMPA 向上计数事件)?

谢谢

获得的波形的区域。 什么不匹配?

所需波形中第二个脉冲后的间隙缺失? 其他脉冲/波形是否匹配?

这意味着顶部 PWM 中 缺少下降事件(CMPA 向上计数事件)?

[/报价]你好 Prarthan、

实际上、 其他脉冲也不匹配。 所需波形中的第一个脉冲短于所获得波形中的第一个脉冲。

第二个脉冲后的间隙确实缺失、这也是问题的一部分、我很难理解原因、但即使这是固定的、脉冲长度仍然不匹配。

总之、所需的波形未显示。 我尝试将载波相移改变 180 度、但也没有效果。感谢您的帮助!

您好 Joe、

就是这样。

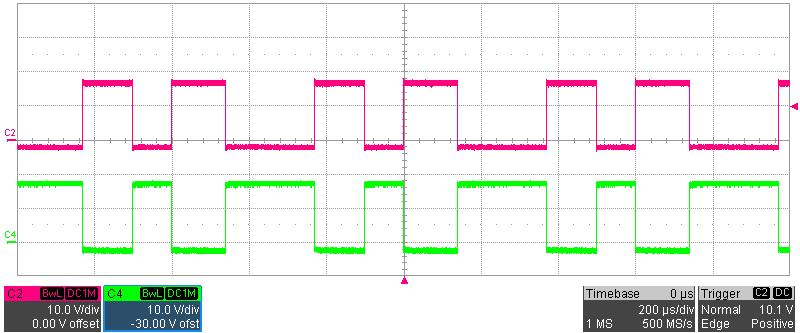

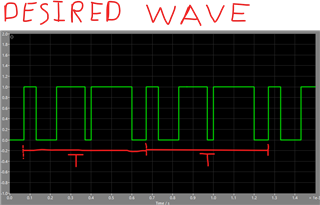

我将占空比降低到 0.9999、现在我得到了所需的波形、完全符合预期。

但是、这会 在另一个波形中产生另一个问题、即使用载波相移 180 度的波形:由于 CMPA 需要小于 PRD、因此复制占空比的合适方法是>= 1、这意味着完全打开/高电平 PWM 信号?

180 度偏移的波形现在面临一个非常小的尖峰、这与波在 PLECS 中越过载波顶部的确切时刻相匹配。

之前:

之后:

您好 Henrique、

此 PWM 模块非常灵活、可通过多种方式进行配置来满足您的需求:

我认为、只要周期事件配置为使引脚也变为低电平、就可以通过允许 100%的占空比来消除干扰 — 确保 CMPA 被削波到 PRD。

而且、在当前设计中、脉冲应以零为中心、从 CTR eq 零事件上的影子加载 CMP 将产生不均匀/不良的脉冲宽度。 将 CMP 影子加载事件更改为 CTR eq PRD 以生成干净脉冲。

您好 Joe、

并且、脉冲应在当前设计中以零为中心、从 Shadow on CTR eq zero 事件加载 CMP 将产生不均匀/不需要的脉冲宽度。 将 CMP 影子加载事件更改为 CTR eq PRD 以生成干净脉冲。

我尝试将 CMP 影子加载设置为等于 PRD、但不能正常使用。 我还查看了数据表、似乎实际上可能的值大于 TBPRD、但在实现这些功能时、UC 似乎不会生成适当的响应。

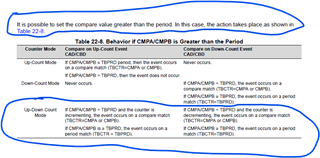

数据表中甚至说 “如果 CMPA/CMPB≥TBPRD、则会在 A 上发生事件

周期匹配 (TBCTR = TBPRD)。“ 因此在我之前的例子中、将占空比设置为 1.1 来强制设置为高电平应该可以根据数据表来实现、不应该吗?

我尝试将 CMP 阴影加载设置为等于 PRD、但无法正常使用。 我还查看了数据表、似乎实际上可能的值大于 TBPRD、但在实现这些功能时、UC 似乎不会生成适当的响应。

[/报价]TRM 是一个很好的参考、可同时尝试执行以下所有步骤:

1.将 CMPx 限制为 PRD

2.设置 PRD 事件可将引脚设置为低电平、此外还可设置 CMP dn/up 事件可将引脚设置为高电平/低电平

3.仅从 PRD 上的影子事件中选择“CMP LOAD“