请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F28388D 工具/软件:

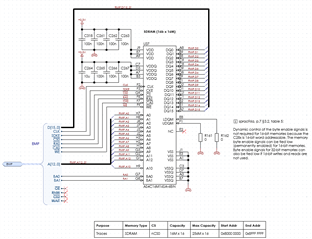

这个线程遵循 这个线程。 我们设计了一个基于 f28388d 的定制电路板、该电路板使用 EMIF2 而不是 EMIF1 来连接 SDRAM。 我们使用了 F28379D_EMIF_DC 参考设计中的确切原理图。 遗憾的是、这种设计 似乎不再投入生产、我们无法使用 LaunchPad 在 EMIF1 上对其进行测试。 此外、该设计被宣布与 f28379d 兼容、而不是 f28388d。 大多数与 EMIF 相关的或相关文档都在 f28388d 之前发布。

我们使用以下原理图进行记录:

使用以下代码配置 SDRAM:

void configure_sdram(){

// Do not synchronize the EMIF2 pins

for (unsigned i = 53; i <= 68; i++){

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

GPIO_setPinConfig(GPIO_68_EMIF2_D0);

GPIO_setPinConfig(GPIO_67_EMIF2_D1);

GPIO_setPinConfig(GPIO_66_EMIF2_D2);

GPIO_setPinConfig(GPIO_65_EMIF2_D3);

GPIO_setPinConfig(GPIO_64_EMIF2_D4);

GPIO_setPinConfig(GPIO_63_EMIF2_D5);

GPIO_setPinConfig(GPIO_62_EMIF2_D6);

GPIO_setPinConfig(GPIO_61_EMIF2_D7);

GPIO_setPinConfig(GPIO_60_EMIF2_D8);

GPIO_setPinConfig(GPIO_59_EMIF2_D9);

GPIO_setPinConfig(GPIO_58_EMIF2_D10);

GPIO_setPinConfig(GPIO_57_EMIF2_D11);

GPIO_setPinConfig(GPIO_56_EMIF2_D12);

GPIO_setPinConfig(GPIO_55_EMIF2_D13);

GPIO_setPinConfig(GPIO_54_EMIF2_D14);

GPIO_setPinConfig(GPIO_53_EMIF2_D15);

GPIO_setPinConfig(GPIO_98_EMIF2_A0);

GPIO_setPinConfig(GPIO_99_EMIF2_A1);

GPIO_setPinConfig(GPIO_100_EMIF2_A2);

GPIO_setPinConfig(GPIO_101_EMIF2_A3);

GPIO_setPinConfig(GPIO_102_EMIF2_A4);

GPIO_setPinConfig(GPIO_103_EMIF2_A5);

GPIO_setPinConfig(GPIO_104_EMIF2_A6);

GPIO_setPinConfig(GPIO_105_EMIF2_A7);

GPIO_setPinConfig(GPIO_106_EMIF2_A8);

GPIO_setPinConfig(GPIO_107_EMIF2_A9);

GPIO_setPinConfig(GPIO_108_EMIF2_A10);

GPIO_setPinConfig(GPIO_109_EMIF2_A11);

GPIO_setPinConfig(GPIO_95_EMIF2_A12);

GPIO_setPinConfig(GPIO_111_EMIF2_BA0);

GPIO_setPinConfig(GPIO_112_EMIF2_BA1);

GPIO_setPinConfig(GPIO_113_EMIF2_CAS);

GPIO_setPinConfig(GPIO_114_EMIF2_RAS);

GPIO_setPinConfig(GPIO_115_EMIF2_CS0N);

GPIO_setPinConfig(GPIO_117_EMIF2_SDCKE);

GPIO_setPinConfig(GPIO_118_EMIF2_CLK);

GPIO_setPinConfig(GPIO_120_EMIF2_WEN);

SysCtl_setEMIF2ClockDivider(SYSCTL_EMIF2CLK_DIV_2);

EMIF_setAccessProtection(EMIF2CONFIG_BASE, 0x0);

EMIF_commitAccessConfig(EMIF2CONFIG_BASE);

EMIF_lockAccessConfig(EMIF2CONFIG_BASE);

// Apply timing parameters

EMIF_SyncTimingParams syncTimingParams;

syncTimingParams.tRfc = 6; // Refresh to Active/Refresh command delay

syncTimingParams.tRp = 1; // Precharge to Activate delay

syncTimingParams.tRcd = 1; // Activate to Read/Write delay

syncTimingParams.tWr = 2; // Write recovery time

syncTimingParams.tRas = 4; // Active to Precharge delay

syncTimingParams.tRc = 6; // Active to Active/Auto Refresh delay

syncTimingParams.tRrd = 1; // Activate to Activate delay (different banks)

EMIF_setSyncTimingParams(EMIF2_BASE, &syncTimingParams);

EMIF_setSyncSelfRefreshExitTmng(EMIF2_BASE, 0x6U);

EMIF_setSyncRefreshRate(EMIF2_BASE, 781);

EMIF_SyncConfig syncConfig;

syncConfig.casLatency = EMIF_SYNC_CAS_LAT_3;

syncConfig.iBank = EMIF_SYNC_BANK_4;

syncConfig.narrowMode = EMIF_SYNC_NARROW_MODE_TRUE;

syncConfig.pageSize = EMIF_SYNC_COLUMN_WIDTH_9;

EMIF_setSyncMemoryConfig(EMIF2_BASE, &syncConfig);

}

为了测试 SDRAM、我们使用以下代码片段:

void test_sdram(){

for (uint32_t k = 0, i = 0; k < MEM_BUFFER_SIZE; k += 1, i += 5) {

extSDRAMBuf[k] = i;

}

for (uint32_t k = 0, i = 0; k < MEM_BUFFER_SIZE; k += 1, i += 5){

if (extSDRAMBuf[k] != i) {

testPass = false;

return;

}

testPass = true;

}

}

使用 32 位缓冲区时、这些值将被正确写入和读回:

0, 5, 10 , 15

但是、当使用 16 位缓冲区时、该值会变得不一致:

5, 5, 15, 15

我们还注意到 memcpy_fast_far 有一些奇怪的用法:

- FAST 观测器 读取 将数据从 SDRAM 传输到本地缓冲区、则值正确。

- FAST 观测器 写入 数据到 SDRAM 时、无论缓冲区是 16 位还是 32 位宽、这些值仍然不一致。

因此、我们的问题是:

- 在访问具有 16 位缓冲器的 SDRAM 时、这是否是 EMIF2 接口的已知限制或行为?

- 我们的 16 位访问配置中是否存在错误或缺失?

- 为什么使用 memcpy_fast_far 进行读取是有效的、但写入却不有效?