请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:F29H850TU工具/软件:

创建新问题作为对我的 原始问题的答复 不能解决我的问题。

我的问题专门涉及多核系统的内核 2 或内核 3 上的看门狗计时器实现以及 本主题中讨论的问题。

在多核系统中实现 WDT 是否需要额外的代码来确保内核 2 /内核 3 上的系统复位将从 MAIN 区域重新启动执行?

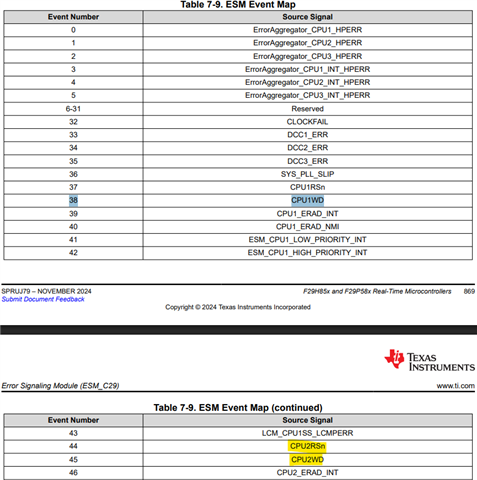

如果我要在 内核 2 或内核 3 中的 WDT 超时时执行系统复位、 是否需要利用 ESM 或 IPC 与 CPU1 通信以执行系统复位?