工具/软件:

尊敬的专家:

我们的客户遇到了以下问题、并有一些问题:

-

MCAN 和 IPC 冲突:

启用 IPC 后、MCAN 初始化失败。 TI 是否提供任何同时支持 MCAN 和 IPC 功能的示例? -

多核数据共享:

客户需要使用 MCAN、因此不使用 IPC 功能。 对于多核数据共享、他们是否应该采取任何预防措施? 在 TI 的示例中、提到了以下代码:void writeDataCPU1 (void)

{

uint16_t 索引;

//

//使用第一个位置编写乘法器。

//

cpu1RWArray[0]=乘法器;

for (INDEX = 1;INDEX < 256;INDEX++)

{

cpu1RWArray[index]= index;

//

//以下代码将尝试写入分配的共享 RAM

//到 CPU2、因此会导致访问违例。

//

// cpu1RArray[index]= 1000 + index;

}

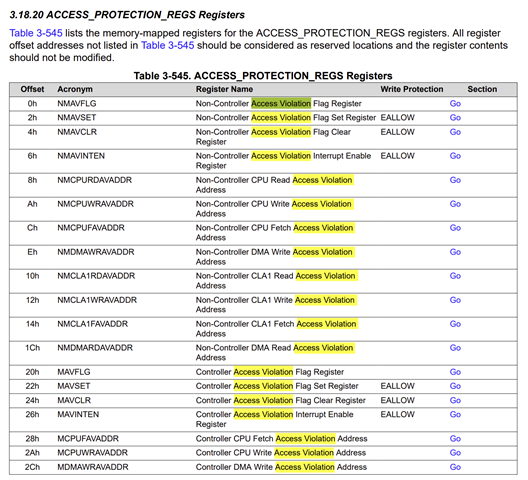

}该示例提到了“访问冲突“。 这是否会导致 CPU 或 CLA 生成可能中断正常系统运行的异常(故障或陷阱)?

-

当前的多核数据共享方法:

客户当前的方法是指定内核之间的读取/写入操作方向、由数据贡献器写入、数据接收器读取。 除了数据不能实时更新的问题外、这种方法是否存在其他潜在风险?