工具/软件:

我正在处理的 “single_axis_servo_drive_fcl_QEP_f28p65x"</s>“ 工程。

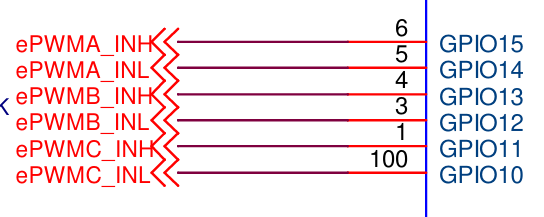

在最初进行评估时、我选择了 Launch-XL-F28P65X LaunchPad、并使用了具有 169 引脚的 NMR 封装。 对于定制电路板 、我们采用了 TMS320F28P659DK8-Q1、它是 100 引脚型号 (PZP)。

现在、根据 我的理解、如果配置相同、两个控制器的 PWM 输出必须相同。 在这里、我们得到的输出完全相反。

因此、我仅实现了具有 50%占空比的 PWM 配置、以便在两个具有相同配置的硬件上进行测试。

这是 PWM 的配置。

我使用的是加/减计数器、TBCTR==TBPRD 时的中断、

在向上计数期间、当 TBCTR =CMPA 时、输出引脚变为低电平、在 TBCTR =CMPA 时、输出引脚变为高电平。

void configurePWM(void)

{

uint16_t base;

SysCtl_disablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

// *****************************************

// Inverter PWM configuration - PWM 1, 2, 3

// *****************************************

for (base = 0; base < 3; base++)

{

// Time Base SubModule Registers

// set Immediate load

EPWM_setPeriodLoadMode(pwmHandle[base], EPWM_PERIOD_DIRECT_LOAD);

EPWM_setTimeBasePeriod(pwmHandle[base], INV_PWM_TICKS / 2);

EPWM_setPhaseShift(pwmHandle[base], 0);

EPWM_setTimeBaseCounter(pwmHandle[base], 0);

EPWM_setTimeBaseCounterMode(pwmHandle[base], EPWM_COUNTER_MODE_UP_DOWN);

EPWM_setClockPrescaler(pwmHandle[base], EPWM_CLOCK_DIVIDER_1,

EPWM_HSCLOCK_DIVIDER_1);

EPWM_disablePhaseShiftLoad(pwmHandle[base]);

// sync "down-stream"

EPWM_enableSyncOutPulseSource(pwmHandle[base],

EPWM_SYNC_OUT_PULSE_ON_CNTR_ZERO);

// Counter Compare Submodule Registers

// set duty 0% initially

EPWM_setCounterCompareValue(pwmHandle[base], EPWM_COUNTER_COMPARE_A, 0);

EPWM_setCounterCompareShadowLoadMode(pwmHandle[base],

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

)

// Action Qualifier SubModule Registers

EPWM_setActionQualifierActionComplete(

pwmHandle[base],

EPWM_AQ_OUTPUT_A,

(EPWM_ActionQualifierEventAction) (EPWM_AQ_OUTPUT_LOW_UP_CMPA

| EPWM_AQ_OUTPUT_HIGH_DOWN_CMPA));

// Active high complementary PWMs - Set up the deadband

EPWM_setRisingEdgeDeadBandDelayInput(pwmHandle[base],

EPWM_DB_INPUT_EPWMA);

EPWM_setFallingEdgeDeadBandDelayInput(pwmHandle[base],

EPWM_DB_INPUT_EPWMA);

EPWM_setDeadBandDelayMode(pwmHandle[base], EPWM_DB_RED, true);

EPWM_setDeadBandDelayMode(pwmHandle[base], EPWM_DB_FED, true);

EPWM_setDeadBandDelayPolarity(pwmHandle[base], EPWM_DB_RED,

EPWM_DB_POLARITY_ACTIVE_HIGH);

EPWM_setDeadBandDelayPolarity(pwmHandle[base], EPWM_DB_FED,

EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setRisingEdgeDelayCount(pwmHandle[base], INV_PWM_DB);

EPWM_setFallingEdgeDelayCount(pwmHandle[base], INV_PWM_DB);

}

// // configure V and W as slaves

EPWM_setSyncInPulseSource(MTR_V_PWM_BASE, PWM_SYNC_SOURCE);

EPWM_enablePhaseShiftLoad(MTR_V_PWM_BASE);

EPWM_setPhaseShift(MTR_V_PWM_BASE, 2);

EPWM_setCountModeAfterSync(MTR_V_PWM_BASE, EPWM_COUNT_MODE_UP_AFTER_SYNC);

EPWM_setSyncInPulseSource(MTR_W_PWM_BASE, PWM_SYNC_SOURCE);

EPWM_enablePhaseShiftLoad(MTR_W_PWM_BASE);

EPWM_setPhaseShift(MTR_W_PWM_BASE, 2);

EPWM_setCountModeAfterSync(MTR_W_PWM_BASE, EPWM_COUNT_MODE_UP_AFTER_SYNC);

SysCtl_disablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

return;

}

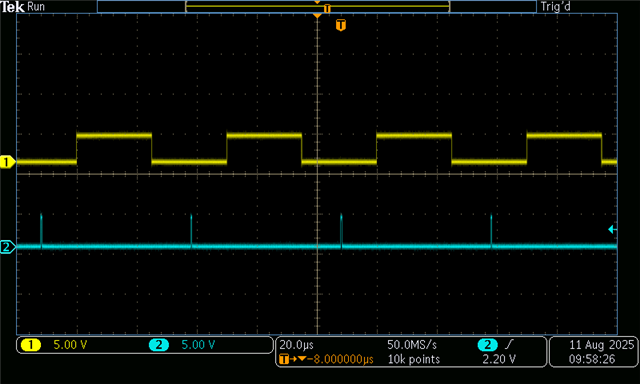

以下是 来自同一配置下两个控制器的探测输出。 黄色

在这里、黄色是占空比为 50%的 EPWMxA、粉色是 GPIO 引脚每 TBCTR=TBPRD 变为高电平、此处的 TBPRD 为 2500。(硬编码用于测试)

从逻辑上讲、定制电路板输出是我想的正确输出。

是否缺少任何配置?

谢谢。此致

Raghu。