工具/软件:

您好:

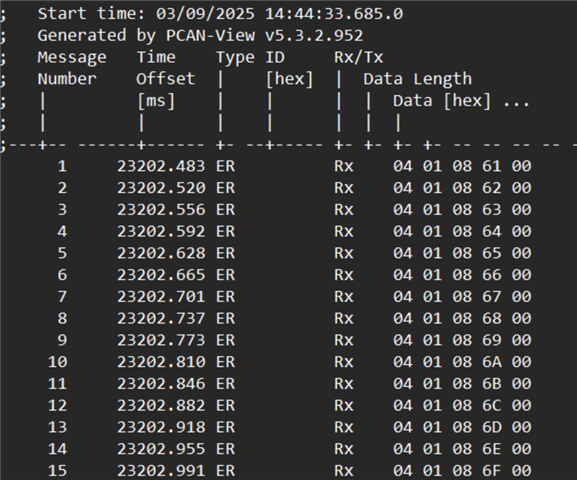

我们目前有一款产品在 1MHz 和 5MHz 分别针对标称比特率和数据比特率运行 CAN 网络。 我们使用 40MHHz 的 MCAN 时钟和 120MHz 的 SYSCLK。 但是、我们打算增加网络节点总数、我们想知道是否可以将 CAN 速度至少提高到 2MHz 和 8MHz(标称比特率和数据比特率)。但是、我们对该模块有很多问题。

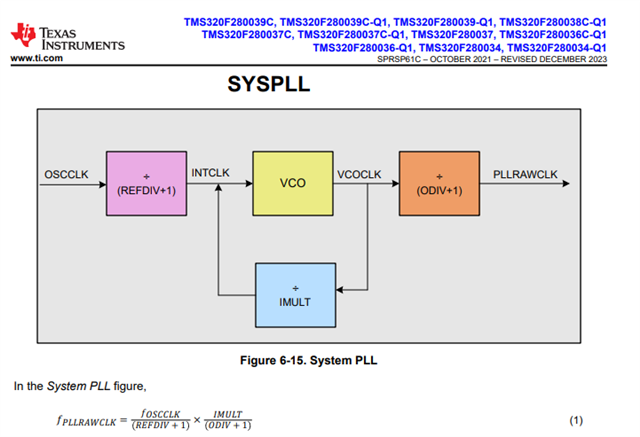

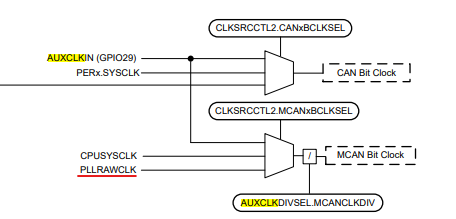

-我们希望将 MCAN 时钟增加到 120MHz、以便 CAN 位时间计算器可以为我们提供在 MCAN 模块中使用的可行配置。 这会产生任何问题吗? th MCAN 模块是否需要比应用程序代码慢才能正常工作? 如果是、关于该应用程序与 MCAN 相比速度有多快、应遵循哪条适当的经验法则?

-它是强制使用时钟值,如在 PCAN 中找到的值,甚至在 CAN 标准,如 80MHz , 60MHz 等?

-如果不可能使用 120MHz 作为 MCAN 时钟,有没有办法有一个标准值的时钟,如 80MHz 无需具有更快的 SYSCLK?

- 2 个不同的节点可以在不同的 MCAN 时钟速度的同一 CAN 网络中共存吗? 采样点与 2 个不同节点之间的差异有多大? 如果是、为了实现与不同 MCAN 时钟的可靠通信、最重要的参数是什么?

此致、

David