工具/软件:

您好专家

客户反馈他们发现 PWM CTR =零中断触发延迟未修复。 测试方法是、它们是设置的 AQ 块 PWM 在 CTR = ZERO 时设置为高电平、 同时、设置 A PWM 中的 GPIO 为高电平 CTR= ZERO 中断 、并发现 2 个输出之间的上升边沿间隔在每个触发器中是不同的:

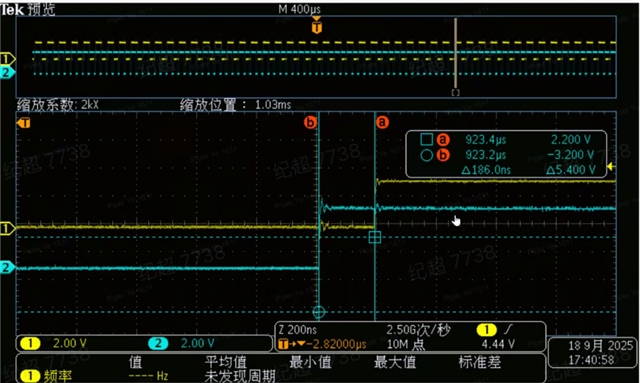

- 您可以看到第 1 个间隔为 186ns:

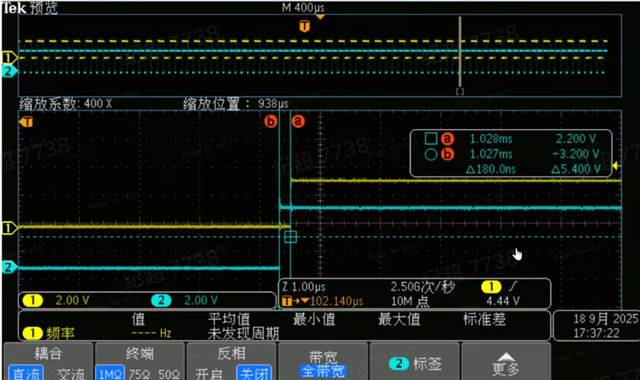

- 第二个间隔为 180ns

- 还有一个 400ns 的间隔、但没有图像反馈。

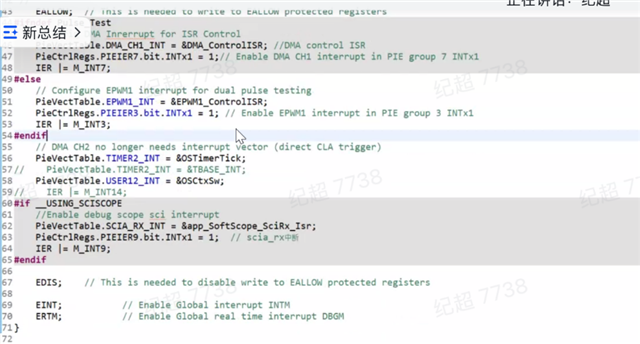

代码中只有 PWM 中断、没有其他中断阻止 PWM 中断:

请帮助您了解为什么会发生此间隔、以及时间间隔中为什么会出现抖动?

谢谢

Joe