Other Parts Discussed in Thread: SYSCONFIG

器件型号: TMS320F28P550SJ

主题: SysConfig 中讨论的其他器件

您好:

我一直致力于将 bissc 库从 f28p65x 改编为 f28p55x、并且做了非常小的更改。 CLB 逻辑块设计协同响应如下:

- CLB4 65x - CLB2 55x

- CLB3 65x - CLB1 55x

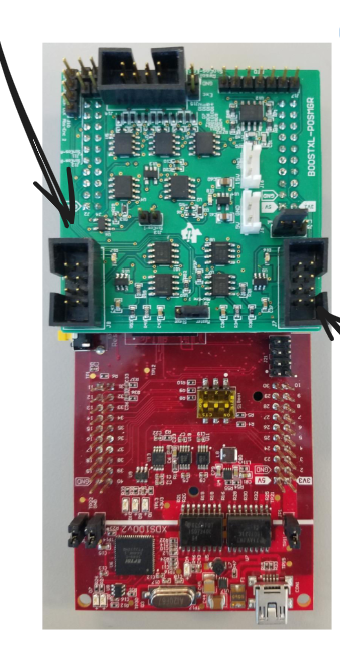

这会导致 MA 输出出现问题、该输出必须位于 GPIO2 中以避免超过配置、然后跳线电缆连接到 GPIO12 硬件看起来像这样:

一些测试后、我可以看到 MA 时钟没有输出我计算出的 CLK 频率:

- 我想要一个 5MHz Ma lcock

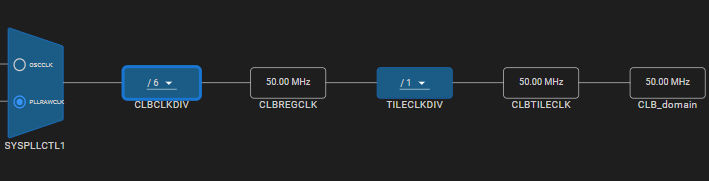

- SysConfig 工具中的 CLB 时钟显示我使用的是 50MHz。 我尝试将预分频器修改为用户 100MHz、但我无法看到 MA 时钟的任何变化。

- CLB FREQ_DIVIDER 为 5。 此值输入到匹配的复印机值。

结果是 MA 信号为 3MHz。 我一直在调节预分频器、PLL 分频器等、无法修改 MA 时钟周期

哪些参数会对 MA 时钟产生直接影响? 尽管通过更改 CLB CLKDIV、我会获得一些结果、但似乎没有效果。 我在工程中为 CLB 附加了时钟树

最后、我还想解串为什么我在输出端看到的时钟周期大约是我通过 bissc init 函数配置的周期的一半。

此致、

David