部件号: TMS320C5535

大家好!

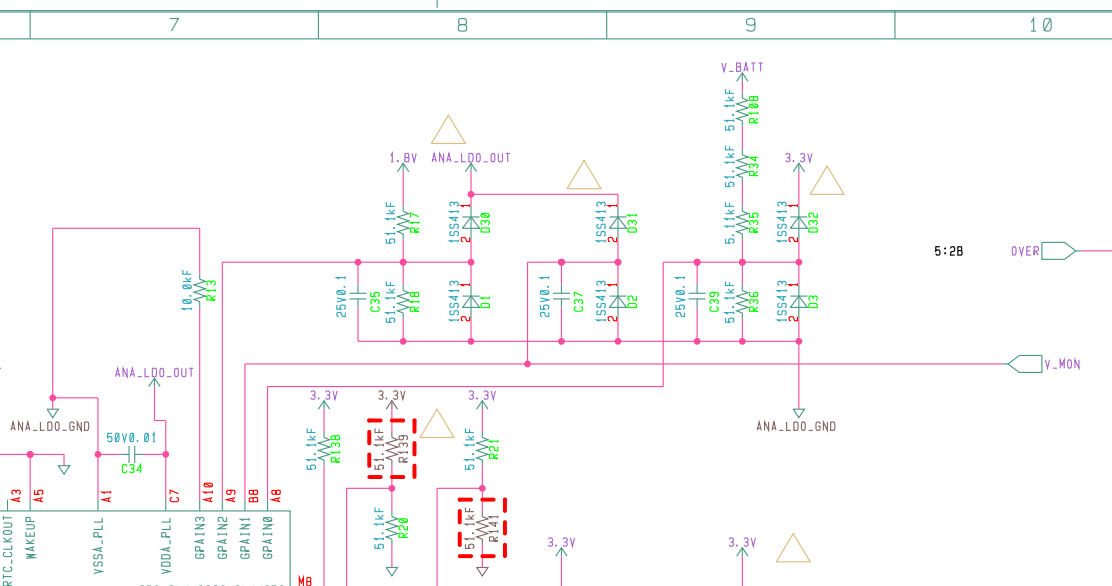

我们使用引脚 GPAIN0–2 来监控 1.8V 等电压和产品的电池电平 (4V–7V)。

但是、有时电池电量显示正确、有时显示不正确。

检查来自 DSP 的 AD 值时、我们会看到一些情况、即即使没有输入、偏移量也约为 10 个计数、以及读数同时存在偏移和变化(也包括大约 0–10 个计数)的情况。

我们目前正在调查造成这种现象的原因。

最初、我们怀疑存在安装缺陷、但 X 射线检查确认组件没有问题。

下面是相关部分的原理图。

您看到此电路中有任何错误吗?

此外、您过去是否遇到过类似的问题?

如果您对调查根本原因的方法有任何建议、请告知我们。

此致、

ITO