器件型号: TMS320F28377D

尊敬的团队:

客户询问 PERIx 的 CLK 频率。 LSPCLK 处于引导顺序。

您能否提供为 PERIx 设置的 CLK 值? LSPCLK?

外部 CLK 输入为 20MHz。

谢谢。此致、

哈拉

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: TMS320F28377D

尊敬的团队:

客户询问 PERIx 的 CLK 频率。 LSPCLK 处于引导顺序。

您能否提供为 PERIx 设置的 CLK 值? LSPCLK?

外部 CLK 输入为 20MHz。

谢谢。此致、

哈拉

尊敬的 Hara:

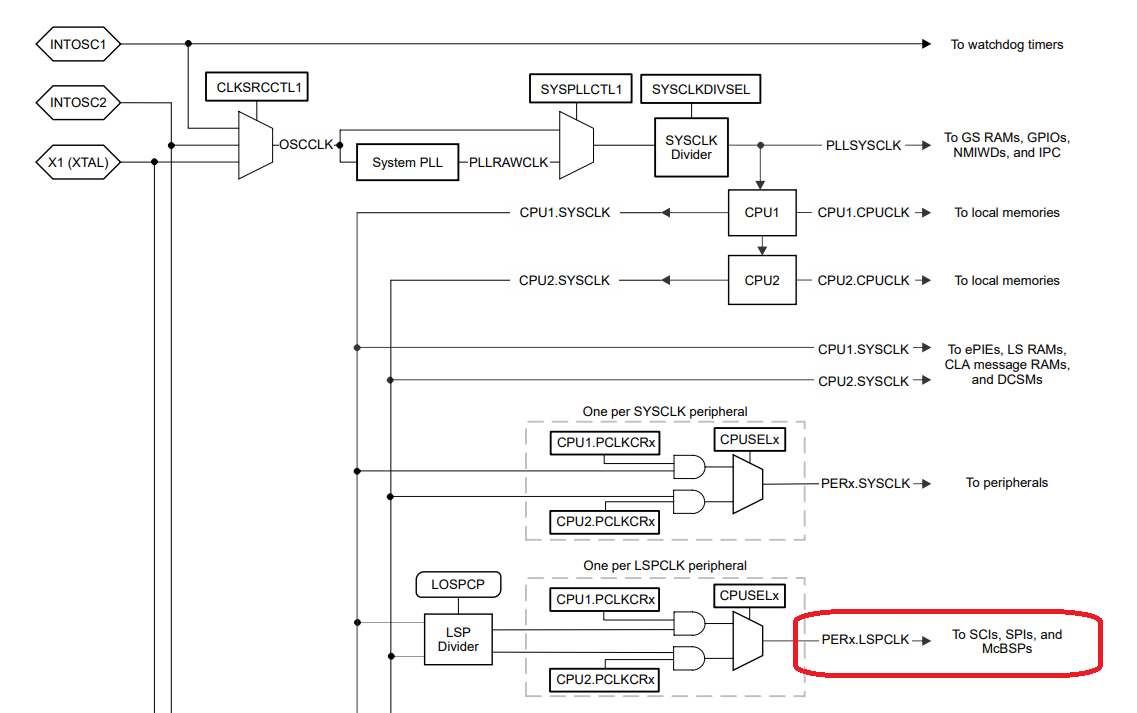

在引导期间、不使用 PLL、仅使用 INTOSC2。 在 SCI/SPI 引导中、 LOSPCP 设置为/4、更多详细信息请参见 第 4 章。

默认 LOSPCP(低速时钟源预分频)设置为/2、即 SYSCLK / 2。 在 POR 时、SYSCLKDIVSEL 为/1、这意味着 LSPCLK 默认为 5MHz(除非处于 SCI/SPI 引导状态)。

此致、

Aishwarya

尊敬的 Aishwarya:

以下是其他问题。 您还能检查一下这些内容吗?

问题 1: 在 SCI 引导序列时、这些正确理解吗?

INTOSC2:10MHz

LSPCLK:2.5MHz ( SCI 引导序列上的 LOSPCP /4)

问题 2: SCI 引导序列上的 CLK 树

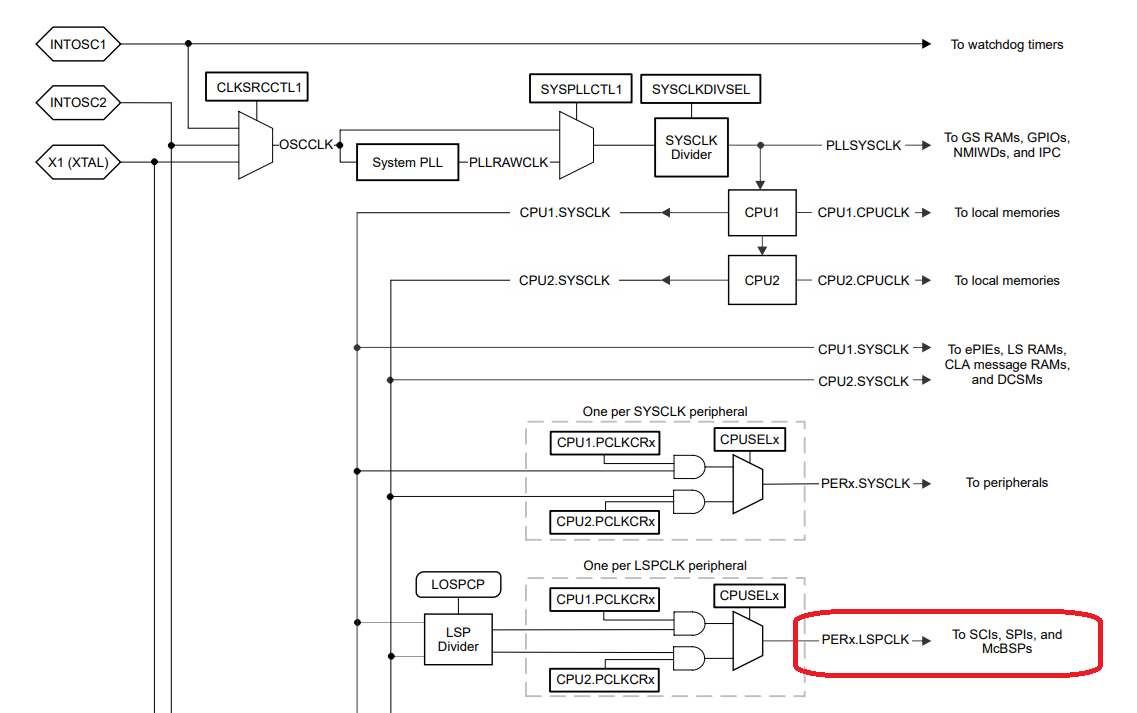

根据 4.8 注释、只使用 INTOSC 来代替 PLL。

下图中有一条通过 PLL 的路由、但存在一个问题、即 SYSCLK 分频器将后跟 SYSCLKDIVSEL /4 的初始值。

它是否识别出 SYSCLK 分频器在 SCI 引导序列下通过?

问题 3 具有自动波特率检测功能的波特率设置、这种正确理解是否正确?

SCI 异步波特率= LSPCLK /((BRR + 1)*8)

*基于 19.15.2.3 SCIHBAUD 寄存器(偏移= 2h)[复位= 0000h

谢谢。此致、

哈拉

HARA、

对于#1、正确。

对于#2、无论是否绕过 PLL、始终应用 SYSCLKDIVSEL。 如前面所述并如引导序列映像所示、时钟分频器配置在器件复位后发生。 表 4.9.1 复位原因和处理详细信息每次复位的引导 ROM 操作。 在 POR、XRSn 等情况下、SYSCLKDIVSEL 为/1 而不是/4。 这适用于所有引导模式。

对于#3、 正确、但请记住 SCI 时钟!= SCI 波特率。

此致、

Aishwarya