主题中讨论的其他器件: C2000WARE

尊敬的 TI:

我正在尝试调试 TMS320F28384S 控制器上的多个内核(CPU1和 CM)、但 调试连接管理器(CM)内核时遇到问题。 每次加载程序并在 CPU1上单步执行代码都能完美地工作。 但是、在 CM 上加载程序后、它会转到 boot.asm、而不是在 main 处中断。 这会阻止我单步执行 CM 代码、因为无法从 boot.asm 文件中退出。 我无法使其在 main 处中断、当我添加断点时、它会弹出一个"所有资源都在使用中"错误。

这些是我尝试调试 CM 内核的步骤、但我很幸运。

1. 选择要调试的 C28x 应用程序

2. 连接 CM

3.加载符号,然后加载程序

当我第一次执行这些步骤时、它可以正常工作、并且在 CM 中的 main 开始处断路、但在第二次或第三次调试之后、它停止工作、此后我无法使其正常工作。

我正在使用 Blackhawk XDS200调试探针、但我也遇到了与 XDS100相同的问题。

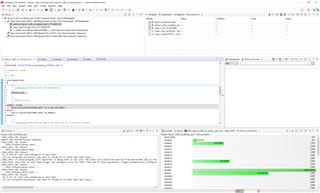

调试 CPU1工作正常、如下所示:

连接到 CM 后、我会加载符号和程序(如下图所示)。 符号似乎加载不正确、我不确定原因是什么?

当尝试向程序添加断点时、会出现以下错误消息:

当我复位 CPU 并重新启动程序时、它会在 boot.asm 中停止、而不是在 main 中停止:

有什么帮助或建议会很好?

此致、

Warrick