您好、香榭丽舍

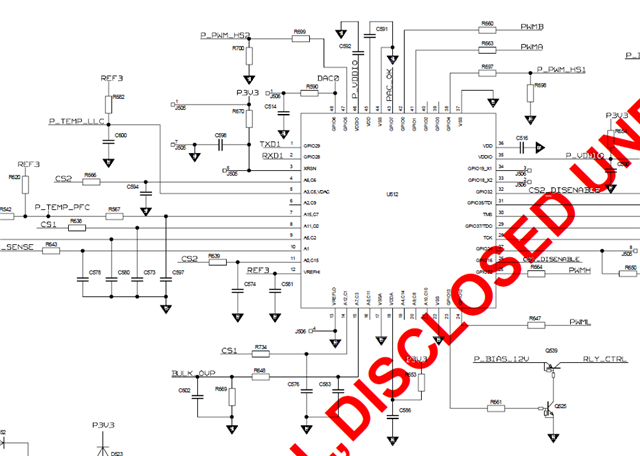

客户将其数字电源平台从 NXP 的 DSP 迁移到 F280023 (PFC)和 F280025 (LLC)。

固件几乎已经完成、单元通过了几乎所有 DVT 功能测试、但它们在浪涌测试中遇到了一些问题。

在2.2KV 差分模式浪涌测试期间、初级 DSP 复位。

主板使用的是旧主板和通过浪涌测试的旧 NXP 平台。 控制板经过重新设计、辅助电源位于控制板上。

-他们使用

-4K7上拉至 XRNS 引脚、并使用10nF 旁路电容、将旁路更改为100nF 无帮助。

-每个 VDDIO 引脚的电容为2.2uF。

-每个 VDD 引脚的电容为10uF。

请分享如何调试和解决此类问题。

谢谢

Tamas