主题中讨论的其他器件: C2000WARE

您好!

我在 TMS320F28379D 上使用 CPU1和 CPU2

在我的软件中、我 想使用 SD 卡上的十六进制文件(使用 SPI-A)对 CPU1和 CPU2的闪存进行重新编程。

如需相关信息、在之前的程序中、我仅使用 CPU1、此函数(使用 SD 卡对闪存重新编程)工作正常。

重新编程过程如下:

- 读取 hex 文件信息

- 擦除 CPU1闪存扇区

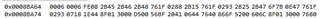

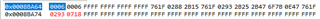

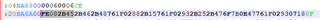

- 在闪存中写入十六进制文件数据

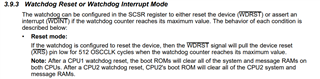

- 使用看门狗重新引导 CPU1

下面是我要继续的方式:

- 在正常状态下、CPU1程序和 CPU2程序与 IPC 标志同步。

- 如果正在对 CPU1进行重新编程、则 CPU2处于"空闲"状态。 SPI-A 由 CPU1驱动。

- 完成 CPU1重新编程后、CPU1向 CPU2发送 IPC (IPC0)标志以开始 重新编程(CPU2上的中断)、更改 SPI-A 所有权(CPU1->CPU2)、然后重新启动。

- CPU2正在重新编程;CPU1处于"空闲"状态。 SPI-A 由 CPU2驱动。

- 完成 CPU2重新编程后、CPU2 将重新启动。

- 当两个内核都将重新启动时、我们将处于正常状态。

我可以正确重新编程 CPU1闪存,但我对 CPU2重新编程有一些疑问:

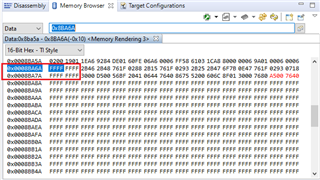

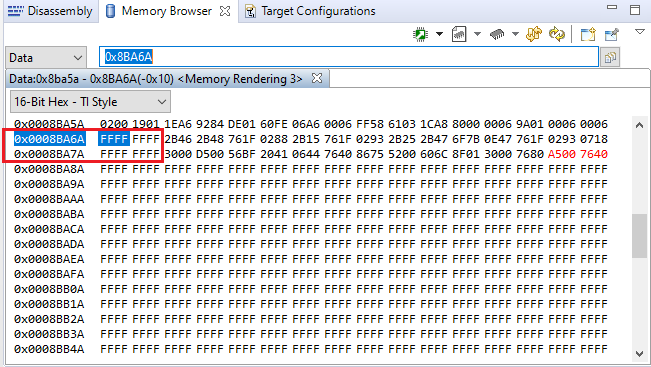

- 在 CPU1闪存编程过程中、CPU1驱动 SPI-A。 在 CPU1重新启动后、我尝试将 SPI-A 所有权更改为 CPU2、但似乎无法正常工作。 为什么?

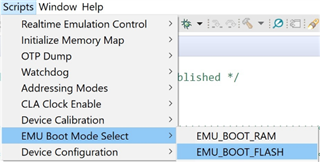

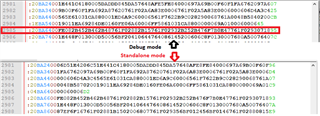

- CPU1编程并重新引导后、我已经有"ILLEGAL_ISR"、这可能是由于重新引导后 Code Composer 上的调试模式造成的。 如何调试 CPU2程序?

此致、