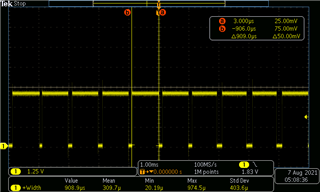

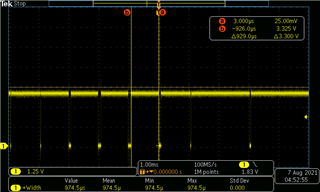

我们在项目中具有激进的中断时序。 ADCINT1和 ADCINT2的采样率均为10us。 ADCINT2的计数器相位设置为5us、这是周期10us 的一半。 它们被指向同一个中断例程。 因此 、ADCINT1和 ADCINT2的中断速率都为5us。 此外、还有其他中断源、例如 HRCAP4_INT。

该工程是使用编译器 v6.1.3构建的、没有问题、工作正常。 但是、 当使用编译器 TIv20.2.4.LTS 进行编译时、处理器停止、代码跳转到 TINT0_ISR ()。

以下是我之前提出的问题、我仍有此问题。