Other Parts Discussed in Thread: SYSCONFIG

Thread 中讨论的其他器件:SysConfig

您好!

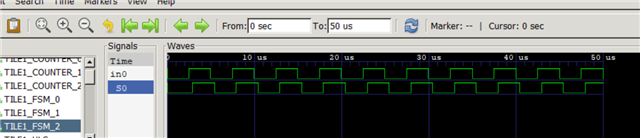

1.是否可以通过 CCS 的 SysConfig 将仿真持续时间设置为50us 或更长时间?

如果可能、请告诉我具体的步骤。

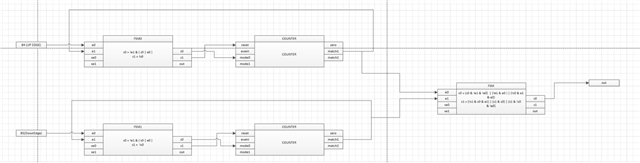

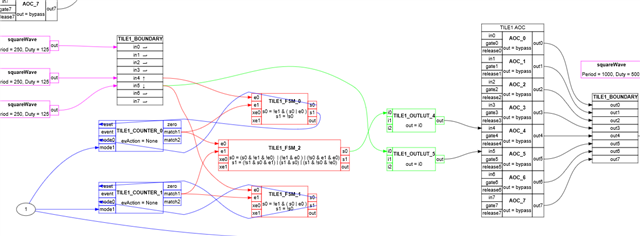

2. 我对如何配置 CLB 有疑问。

我的配置 是在 FSM 后面设置计数器、计数器的输出返回到 FSM。

FSM → 计数 器→FSM

此配置方法是否有任何问题?

请告诉我 是否有任何限制、例如必须将 LUT 设置为计数器输出的后面。

3. 我想执行一个函数来输出相对于 CLB 中输入的延迟输出。

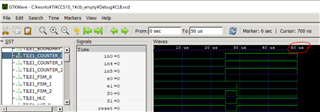

该设计使用以下模块进行仿真。

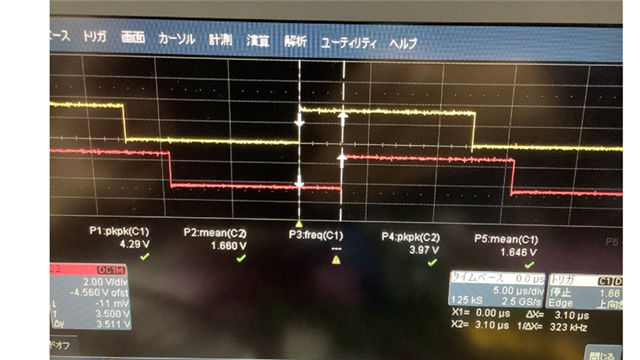

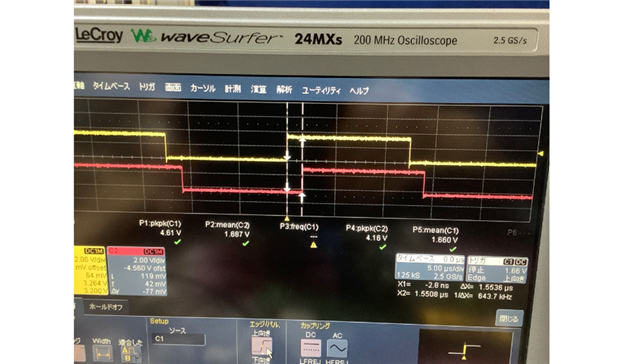

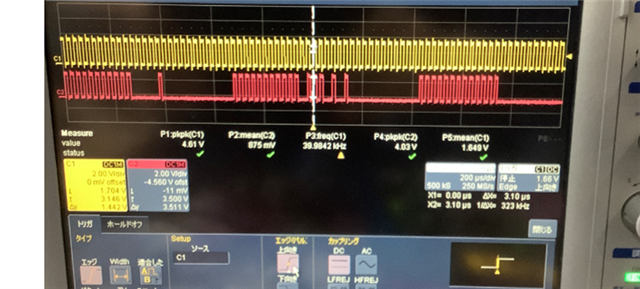

仿真结果如下。

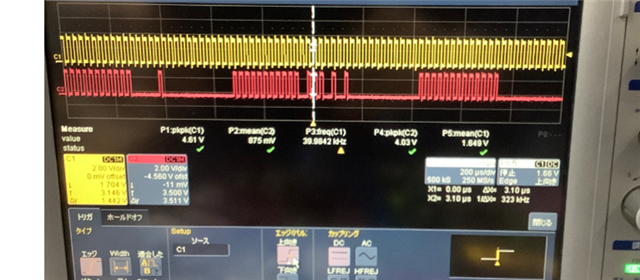

仿真结果和实际操作是不同的。

我希望 CLB 始终以相同的偏差输出、但存在缺少某些波形的现象。

请告诉我如何消除这种现象。

谢谢、

科基