主题中讨论的其他器件:C2000WARE、 ISO7842

现在、我在 c2000ware v3中使用 FSI 示例;使用两个 DSP 进行调试;

现在、我使用这些功能通过 FSI 通道成功进行通信、采用5MHZ 时钟(为什么例程中的默认50MHz 不 起作用、因为50MHz 第一次无法工作);但当我将 FSI 的时钟更改为10MHz 时、无法建立通信

可能的原因是什么? 除了 GPIO 初始化之外、我几乎没有更改示例代码、我使用自己的280049测试板

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

现在、我在 c2000ware v3中使用 FSI 示例;使用两个 DSP 进行调试;

现在、我使用这些功能通过 FSI 通道成功进行通信、采用5MHZ 时钟(为什么例程中的默认50MHz 不 起作用、因为50MHz 第一次无法工作);但当我将 FSI 的时钟更改为10MHz 时、无法建立通信

可能的原因是什么? 除了 GPIO 初始化之外、我几乎没有更改示例代码、我使用自己的280049测试板

您好!

对于高达50MHz 的 FSI 通信、ISO7842的10cm 布线长度应该是可以的。 您在软件中将以下定义设置为什么? 即 DMA 或 CPU 模式?

#define FSI_DMA_ENABLE 0 #define TX_DMA_TRIGGER_ENABLE 0

在10MHz 下测试示例时、主控器件和节点器件是否都通过了握手序列? 如果是、两个器件在握手之后是否都接收到错误、代码执行在'fsirxInt2ISR'中暂停?

最棒的

Kevin

您好!

好的、CPU 模式和常规 DMA 模式(TX_DMA_TRIGGER_ENABLE = 0)应该正常工作、而不会出现任何问题。

[引用 userid="459289" URL"~/support/microcontrollers/c2000/f/c2000-microcontrollers-forum/997630/tms320f280049c-the-problem-of-fsi-example/3689567 #3689567"]我不知道您是否在各种工作条件下运行了这些示例,但当我将其更改为10MHz 时,会定期向领导发送信息,但当汉莎克进程时节点似乎无法接收信息;这些示例已在不同的硬件和不同的运行 FSI 频率下进行了测试。 假设设计中保持良好的信号完整性和通道间偏斜(不使用 FSI RX 偏斜补偿时)、50MHz 下的通信不应成为问题。

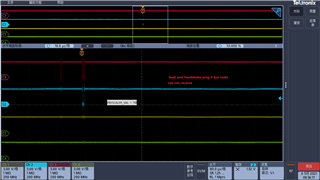

如果 handshake_node ()函数卡在下面的代码行,则节点设备在握手序列期间未从主设备接收到有效的 ping 帧。

while(fsiRxInt1Received != 1);

由于5MHz 频率工作、但10MHz 频率不工作、因此我认为节点 FSI RX 引脚可能存在一些硬件级信号问题。 您能否尝试使用示波器探测节点 FSI RX 引脚上的5MHz 和10MHz 情况信号并进行比较? 对于10MHz 情况、我们希望查看 CLK 和 D0线路的完整性、您可以在此处分享波形的屏幕截图。

最棒的

Kevin

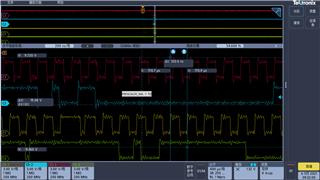

就波形质量而言、没有明显的差异,如果波形质量有影响、我的实际产品是否还需要关注此因素? 这种无法控制的风险有点大

这是我从自己的280049测试板测试的波形、在9MHZ、10MHz、5MHZ 条件下、性能有所不同

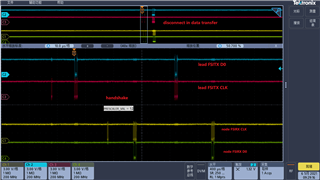

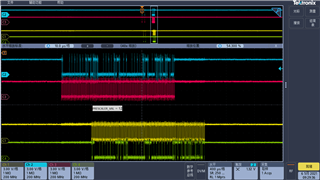

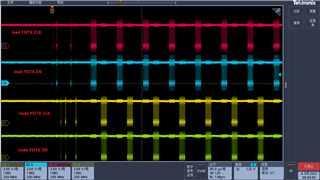

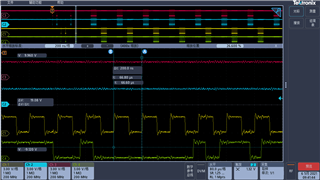

FSI CLK=9MHZ(握手可以完成,但数据通信不能完成)

详细信息:

FSI CLK = 10MHz(握手无法完成)

详细信息:

FSI CLK = 5MHZ(握手和数据传输均正常)

详细信息:

您好!

这很好、您能够找出根本原因。

[引用 userid="459289" URL"~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/997630/tms320f280049c-the-problem-of-fsi-example/3690986 #3690986"]此外、我们是否需要在 FSI 的标准设计中对信号路径进行一些 RC 滤波? 由于 DSP 用于强电干扰场合[/引述]这不是 FSI 通信的要求、但如果您担心高频噪声(>50MHz)、则可以包含具有更高带宽的 RC 滤波。 对于像您一样在单个 PCB 上进行通信的器件、限制 FSI 布线长度并遵循良好的高速信号 PCB 设计实践可能更加重要。

最棒的

Kevin

您好!

成功的 FSI 通信(或任何通信外设的通信外设)将取决于系统运行时线路的信号完整性。 需要在发送器和接收器之间正确保持信号完整性、以便通信正常工作。

[引用 userid="459289" URL"~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/997630/tms320f280049c-the-problem-of-fsi-example/3691887 #3691887"]如果我们考虑 通过30cm 电缆和隔离器在两个单独电路板之间进行通信 时使用 FSI、也是在电源产品条件下、它是否可用于50MHz 通信?对于列出的这些条件、如果在嘈杂的系统环境中电路板之间有一条30cm 的电缆、我们建议您为 FSI 线路使用 LVDS 或 RS-485等差分器件。差分器件将极大地提高 PCB 和电缆上 FSI 线路的抗噪性能、 从而使您能够获得强大的50MHz 通信。

我建议您查看以下页面上的评估板和相关文档、了解有关 FSI +差分器件的一些其他信息。

https://www.ti.com/tool/TMDSFSIADAPEVM

最棒的

Kevin