尊敬的香榭丽舍

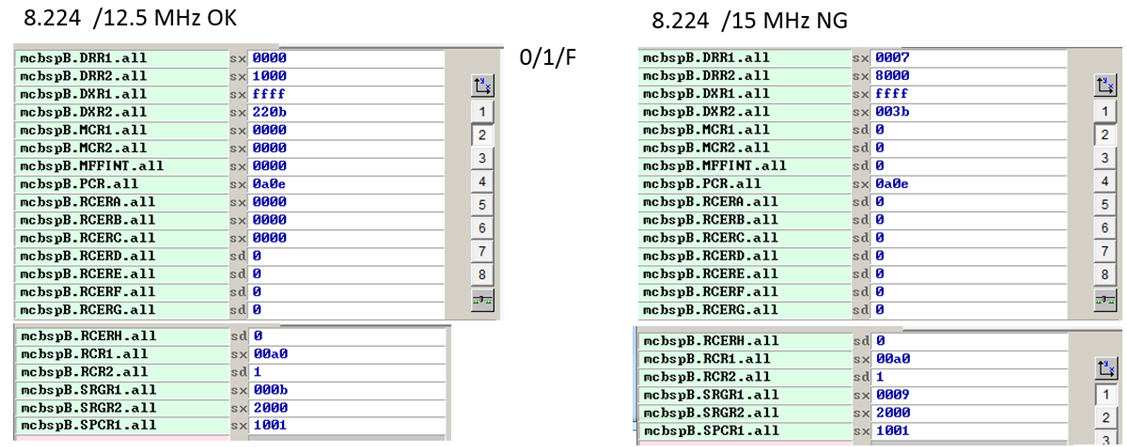

我们通过在 F28335上使用时钟停止模式将 McBSP 用作 SPI 操作。 根据我们设置的寄存器值 mcbspB.SPCR1.all= 0x1001h、对于无时钟延迟的时钟停止模式、它意味着位12-11为10。 这意味着时钟在每次数据传输开始时立即启动(CLKSTP= 10b)。

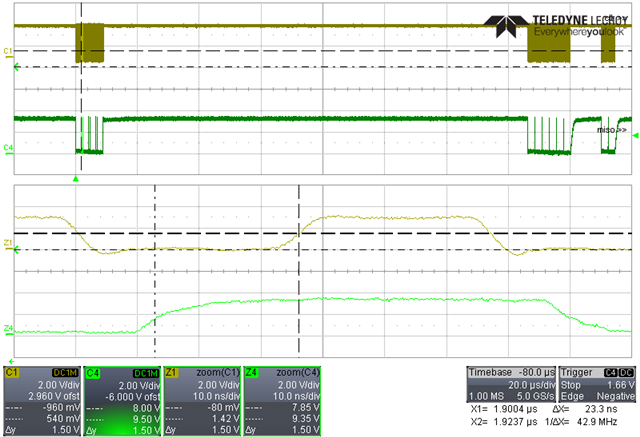

但我们 发现、当 CLKR 为15MHz 时、为了实现正确通信、仍然需要在 RCR2上添加2位数据延迟。

RDATDLY 存在混淆,“在时钟停止模式下,数据延迟值0或2未定义”。

有人知道这种矛盾是什么吗?

如果您有任何建议、请随时告诉我。

非常感谢。

此致、

Janet